TSMCが5nmプロセス・3nmプロセスの詳細を発表、3nmプロセスは2022年下半期に大量生産開始予定

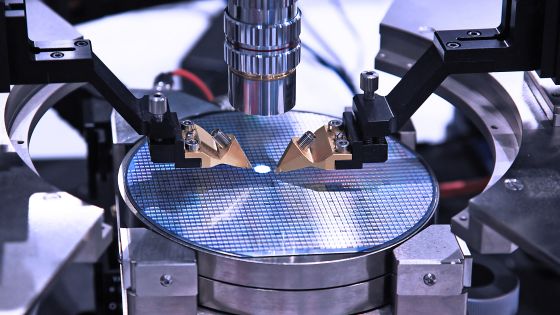

by Steve Jurvetson

大手半導体製造ファウンドリのTSMCが定例技術シンポジウムで、5nmプロセスと3nmプロセスの特徴を解説し、ロードマップと性能予測を発表しました。

‘Better Yield on 5nm than 7nm’: TSMC Update on Defect Rates for N5

https://www.anandtech.com/show/16028/better-yield-on-5nm-than-7nm-tsmc-update-on-defect-rates-for-n5

TSMC Details 3nm Process Technology: Full Node Scaling for 2H22 Volume Production

https://www.anandtech.com/show/16024/tsmc-details-3nm-process-technology-details-full-node-scaling-for-2h22

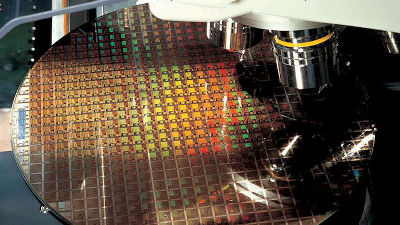

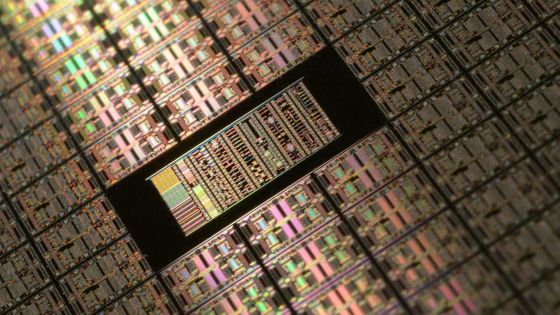

TSMCの5nmプロセスノード「N5」は、極紫外線(EUV)フォトリソグラフィを使ったプロセスノード。EUVフォトリソグラフィは、Huaweiの5G対応SoC・Kirin 990に採用されている7nmプロセスノード「N7+」でも使われている回路パターン生成技術です。

TSMCによれば、N5は7nmプロセスノードの「N7」に比べて、1.8倍のロジック密度、最大15%のパフォーマンス向上、最大30%の電力削減が実現できると主張しています。さらに、N5はN7に比べて高い歩留まりを達成できるとのこと。

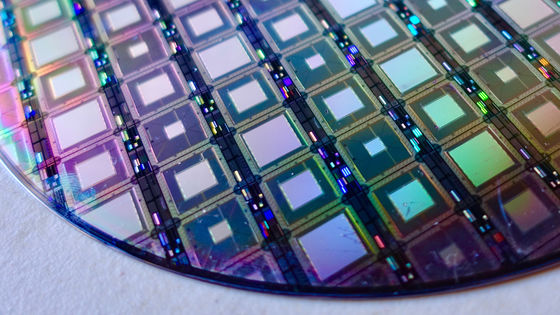

TSMCによればN5を採用した消費者向け製品は2020年中に生産される予定で、技術系ニュースメディアのAnandTechは「Appleの次世代SoCとなるA14チップシリーズで初めてN5が採用される可能性がある」としています。実際に、2020年6月には5nmプロセスの製造が開始されていることが報じられています。

世界最大の半導体製造ファウンドリ「TSMC」が5nmプロセスによる製造を正式に開始 - GIGAZINE

また、TSMCはN5からさらに5%の速度向上と10%の電力削減を目指すプロセスノード「N5P」を2021年に立ち上げる予定と発表。加えて同じ5nmプロセスノードの「N4」は2021年第4四半期にリスク生産に入り、2022年に大量生産に入ると発表しましたが、性能は公表しませんでした。

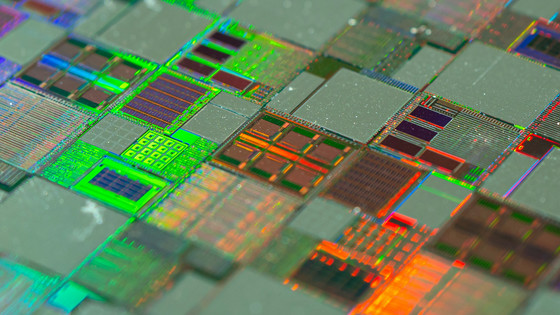

そして、TSMCの3nmプロセスを採用したノード「N3」も発表。N3はN5に比べてパフォーマンスが10~15%向上し、電力消費も25~30%削減されるとのことで、N3は2021年にリスク生産開始が、2022年下半期に大量生産が予定されています。3nmプロセスについては、Samsungが独自のプロセスノード「3GAE」を発表しており、AnandTechは「電力とパフォーマンスについてはN3と3GAEは同等だが、ロジック密度ではN3がかなりリードしている」と評価しています。

なお、以下がTSMCの各ノードの比較をまとめた表です。

プロセスノード (括弧内は比較対象) | N7 (16FF+) | N7 (N10) | N7P (N7) | N7+ (N7) | N5 (N7) | N5P (N5) | N3 (N5) |

| 電力消費 | 60%削減 | 最大40%削減 | 10%削減 | 15%削減 | 30%削減 | 10%削減 | 25~30%削減 |

| パフォーマンス | 30%向上 | ? | 7%向上 | 10%向上 | 15%向上 | 5%向上 | 10~15%向上 |

| シリコンダイ面積 | 70%削減 | 37倍削減 | - | 約17%削減 | 45%削減 (ロジック密度1.8倍) | - | 42%削減 (ロジック密度1.7倍) |

| 大量生産開始時期 | 2019年第2四半期 | 2020年第2四半期 | 2021年 | 2022年下半期 |

・関連記事

Intelの7nmプロセス開発に1年ほどの遅延、CEOはチップ製造の外部委託を検討していると示唆 - GIGAZINE

世界最大の半導体製造ファウンドリ「TSMC」が5nmプロセスによる製造を正式に開始 - GIGAZINE

Appleのチップ製造を担当する世界最大の半導体製造ファウンドリ「TSMC」がアメリカ国内に工場を建設か - GIGAZINE

Huaweiが7nmプロセスのAIプロセッサ「Ascend 910」など発表、将来的にRISC-V採用の可能性も示唆 - GIGAZINE

「ムーアの法則」が減速する中で半導体製造企業の取り組みとは? - GIGAZINE

・関連コンテンツ

in ハードウェア, Posted by log1i_yk

You can read the machine translated English article TSMC announces details of 5nm process/3n….