「ムーアの法則」が減速する中で半導体製造企業の取り組みとは?

by Fritzchens Fritz

「半導体の集積密度は18~24カ月で倍増し、チップの性能が倍になってもさらなる小型化が進む」という経験則が「ムーアの法則」です。しかし、世界最大の半導体製造ファウンドリであるTSMCの会長が「もはやムーアの法則は有効ではない」と発言するなど、近年ムーアの法則に限界が訪れている可能性が浮上しています。世界最大のOSAT(Outsourced Semiconductor Assembly and Test)企業であるASEのエンジニアリング担当ヴァイス・プレジデントのカルヴィン・チャン氏が、半導体について扱うメディア・Semiconductor Engineeringによるインタビューの中で、ムーアの法則について言及しました。

Sidestepping Moore's Law

https://semiengineering.com/sidestepping-moores-law/

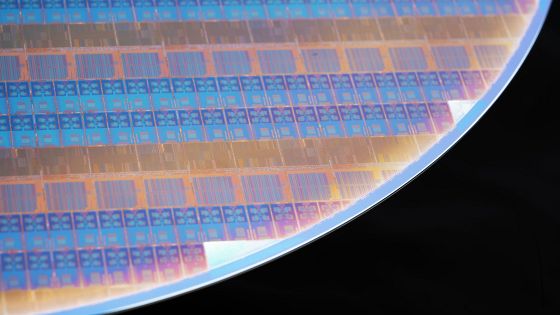

Zen 2アーキテクチャのCPUやRadeon VIIなどのGPUのように、7nmプロセスのチップが一般市場に出回ろうとしていますが、半導体業界はさらなるスケーリングを目指して5nmや3nmプロセスルールの検討をスタート。実際に、2019年4月にはTSMCが5nmプロセスでの製造インフラを完成させたと発表しました。

TSMCが5nmプロセスの先行生産を開始、7nmプロセスから1.8倍のトランジスタ密度と15%の速度上昇を実現 - GIGAZINE

チャン氏は「現代のICのパッケージングにおける大きな問題はなんですか?」という質問に対して「ムーアの法則は減速しています」と断言。一方で、トランジスタのスケーリングは今後も続いていくため、パッケージング業界とOSAT企業はそのギャップを埋めるような技術が求められていると述べました。

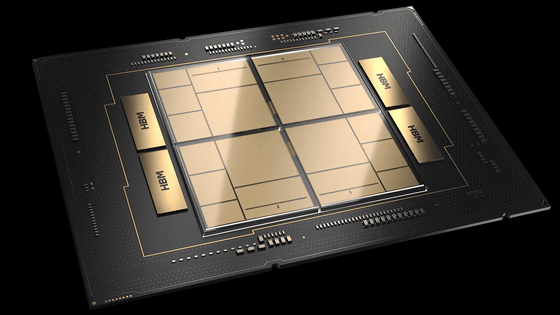

CMOSやMEMSは、7nmプロセスで作成すると非常にコストがかかるとのこと。そこで、CMOSのスケーリングでは、1チップ化せずに複数のLSIチップを1つのパッケージに封止する「System in a Package(SiP)」を採用する方向に業界全体が動いています。

MEMSとCMOSとの最適な集積化によりICの性能向上が明確に - セミコンポータル

https://www.semiconportal.com/archive/editorial/technology/process/090928-memscmos.html

チャン氏は、将来的にはシリコンチップ上に複数の回路を形成して1つのチップで1つのシステムを作り上げるSystem on a chip(SoC)ではなく、SiPを採用した半導体製品が増えるだろうと予想しています。チャン氏は、集積密度をただ上げていくと開発コストと半導体のコストはほとんどの企業にとって厳しいレベルにまで上がっていくと述べ、電力供給・電力効率・相互接続密度を中心とした技術を組み合わせたソリューションを構築する必要性を説きました。

・関連記事

ムーアの法則の限界を突破する「金属-空気トランジスタ」が半導体を置き換える可能性 - GIGAZINE

RISC-Vは「ムーアの法則」以来の技術イノベーションになるとの予想 - GIGAZINE

「ムーアの法則はもう限界」とiPhoneにチップを提供する半導体大手TSMCの会長が発言 - GIGAZINE

「ムーアの法則」の限界を回避できる期待の製造技術「EUVリソグラフィ」とは? - GIGAZINE

「ムーアの法則」の終焉は何を意味するのか? - GIGAZINE

・関連コンテンツ

in ハードウェア, Posted by log1i_yk

You can read the machine translated English article With the slowing of Moore's law, wha….