TSMCが1.6nm世代の半導体製造プロセス「A16」を2026年中に量産開始すると発表

by 李 季霖

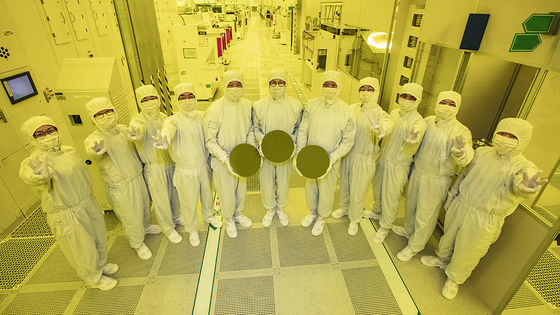

半導体製造企業のTSMCが、2024年4月24日に開催された同社のシンポジウム「North America Technology Symposium 2024」で、1.6nm世代の半導体製造プロセス「A16」の量産を2026年に開始する予定を明らかにしました。

TSMC Celebrates 30th North America Technology Symposium with Innovations Powering AI with Silicon Leadership

https://pr.tsmc.com/japanese/news/3136

TSMC unveils 1.6nm process technology with backside power delivery, rivals Intel's competing design | Tom's Hardware

https://www.tomshardware.com/tech-industry/tsmc-unveils-16nm-process-technology-with-backside-power-delivery-rivals-intels-competing-design

TSMCはA16プロセスを2026年に量産開始する予定です。A16は、すでに量産中である3nm世代の「N3E」と、2025年後半に量産開始となる2nm世代のN2プロセスに続く、次世代のプロセスになります。

TSMCが3nmプロセスの拡張バージョン展開や2nmプロセスの製造技術を正式に発表、2nmプロセスの市場投入は2025年後半か - GIGAZINE

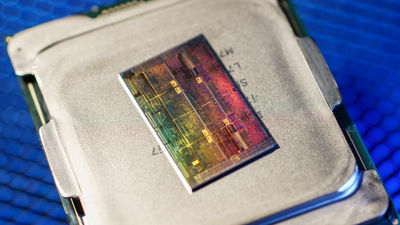

A16は、TSMCの最先端となる「ナノシートトランジスタ」を採用しています。ナノシートトランジスタは、従来のFinFETトランジスタと比較してより優れた電気的特性と制御性を提供するため、トランジスタのサイズを縮小しつつ、性能と電力効率を向上できるのがポイントです。

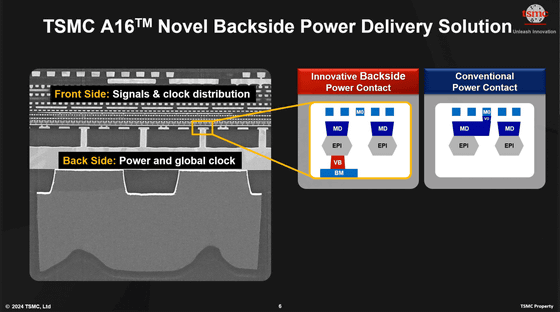

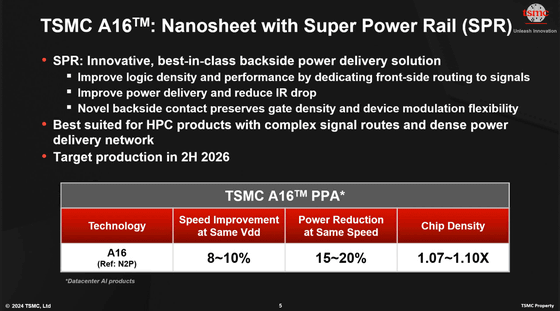

また、A16は、「Super Power Rail」と呼ばれるアーキテクチャを採用しているのが特徴です。このSuper Power Railは、チップの裏面に専用の電力レールを配置することで、電力供給の性能を向上させるというもの。これにより、表面の配線リソースを信号配線に特化できるため、複雑な信号回路が必要な設計に対して有利になります。

A16は高密度の電力供給ネットワークを備えているため、AIアクセラレータのような電力を大量に消費するチップにも適しています。TSMCによると、2nmプロセス世代のN2Pプロセスと比較して、A16は同じVDD(正の電源電圧)で8~10%の速度向上、同じ速度で15~20%の消費電力削減を実現しているそうで、データセンター製品では最大1.10倍のチップ密度向上も可能だとしています。

また、TSMCはN2プロセスに導入予定の技術「TSMC NanoFlex」を発表しました。TSMC NanoFlexは、N2プロセスのスタンダードセルに、面積が小さく優れた電力効率を目指す「ショートセル」とパフォーマンスの最大化を目指す「トールセル」の2種類を用意します。チップの設計者は、高性能を必要とする設計ブロックではトールセルを多用し、低消費電力を重視する部分ではショートセルを多く配置するなど、同一の設計ブロック内でショートセルとトールセルを組み合わせることでアプリケーションごとに最適なパフォーマンスを実現できるようになるとのこと。

加えて、TSMCは5nm世代のN4Pプロセスの拡張版である「N4C」を2025年に量産開始する予定であることを明らかにしました。N4CはN4Pと完全に互換性のあるルールを採用しているため、N4PからN4Cへの移行にかかるコストは最小限に抑えられるというのがポイント。同時にN4CはN4Pと比較して最大8.5%のダイコスト削減を実現し、N4Pと比較して同等の機能を持つチップをより低コストで製造できるようになるとのこと。このコスト削減は、ダイサイズの縮小による歩留まり率の向上によって達成されるとTSMCは述べています。

そして、TSMCは複数のプロセッサコアとHigh Bandwidth Memory(高帯域幅メモリ)スタックを並べて配置する「CoWoS(Chip on Wafer on Substrate)」、複数のチップを垂直に積層することで高密度で高性能なシステムを実現する「SoIC(System on Integrated Chips)」、300mmウェハ上に大規模なダイアレイを配置する「TSMC-SoW(System-on-Wafer)」を発表。いずれも、より高密度で高性能なSoCを設計するための先進パッケージング技術となっています。

TSMCは、AIブームに伴うデータ伝送の爆発的な増加をサポートするために、COUPE(Compact Universal Photonic Engine)という技術を開発しているとのこと。COUPEはシリコンフォトニクス統合技術で、「SoIC-Xチップスタッキング」によってフォトニクスダイの上に電気ダイを積層することでダイ間インターフェースでの最小のインピーダンスを提供し、従来のスタッキング方法と比較してエネルギー効率を向上させます。COUPEは2026年にはCoWoSと統合され、CPO(Co-Packaged Optics)として提供される予定だそうです。

また、TSMCは自動車向けの技術として「InFO-oS」と「CoWoS-R」を発表しました。いずれもTSMCの先進技術を自動車用に適応させたもので、2025年第4四半期までにAEC-Q100 のグレード2認定を取得することを目指しているとのこと。

TSMCのシーシー・ウェイCEOは「私たちは、AIがデータセンターだけでなく、パソコン、モバイル機器、自動車、さらにはモノのインターネットでも稼働する世界を迎えようとしています。TSMCでは、お客様のAIに関するビジョンを実現するために、最も包括的な技術を提供しています。それは、世界最先端のシリコンから最も幅広い先進パッケージングと3D ICプラットフォームのポートフォリオ、そしてデジタルの世界と現実の世界を統合する特殊技術に至るまで及びます」とコメントしました。

◆フォーラム開設中

本記事に関連するフォーラムをGIGAZINE公式Discordサーバーに設置しました。誰でも自由に書き込めるので、どしどしコメントしてください!Discordアカウントを持っていない場合は、アカウント作成手順解説記事を参考にアカウントを作成してみてください!

• Discord | "所持デバイスの中で「最も小さいプロセスルールの半導体」を搭載するデバイスは何?" | GIGAZINE(ギガジン)

https://discord.com/channels/1037961069903216680/1233343036541374514

・関連記事

SK HynixがTSMCとの提携を発表、2026年に量産予定の次世代HBM4チップと高度なチップパッケージング技術の開発へ - GIGAZINE

TSMCが日本での半導体パッケージング工場の建設を検討中との報道 - GIGAZINE

Intel・Samsung・TSMCのチップメーカー3社が未来の3次元トランジスタ構造「CFET」の実証デモを発表 - GIGAZINE

TSMCは日本やアメリカなど台湾以外での半導体生産に割増料金を設定する予定 - GIGAZINE

TSMCの第1四半期の売上高が前年同期比16.5%増の約2兆8000億円に到達、2024年には売上高が20%以上増加し280億~320億ドルの設備投資が見込まれると予想 - GIGAZINE

TSMCがアメリカ政府から1兆円の資金調達に成功してアリゾナ州に3番目の半導体工場を建設することを発表 - GIGAZINE

・関連コンテンツ