With the slowing of Moore's law, what are the efforts of semiconductor manufacturers?

by Fritzchens Fritz

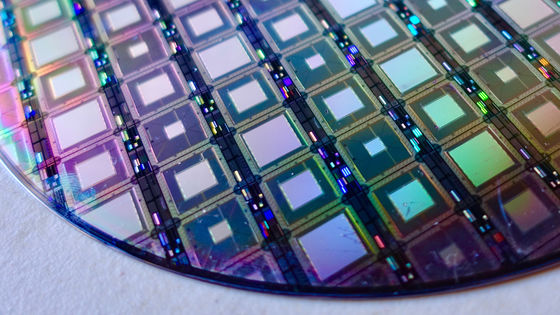

The rule of thumb is that the density of semiconductors doubles in 18 to 24 months, and even if chip performance is doubled, further miniaturization is achieved, the Moore's Law . However, there is a possibility that the Moore's law has reached its limit in recent years, with the chairman of TSMC , the world's largest semiconductor manufacturing foundry, saying 'Moore's law is no longer valid.' The world's largest OSAT (Outsourced Semiconductor Assembly And Test) is a company ASE Mr. Calvin Chan of Engineering Vice-President, the media deals with semiconductor Semiconductor Engineering in an interview by, we refer to Moore's Law.

Sidestepping Moore's Law

https://semiengineering.com/sidestepping-moores-law/

The 7 nm chips are coming to the general market like CPUs of the Zen 2 architecture and GPUs such as the Radeon VII , but the semiconductor industry has started to study the 5 nm and 3 nm process rules for further scaling. In fact, in April 2019, we announced that TSMC completed the manufacturing infrastructure for the 5nm process.

TSMC Starts Preceding Production of 5nm Process, Achieves 1.8x Transistor Density and 15% Speed Increase from 7nm Process-GIGAZINE

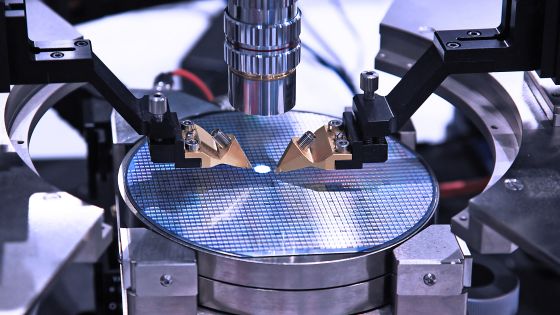

In response to the question, 'What's the big problem in modern IC packaging ?' Mr. Chan affirms that 'Moore's law is slowing down.' At the same time, as transistor scaling continues, the packaging industry and OSAT companies have said that technology is needed to fill the gap.

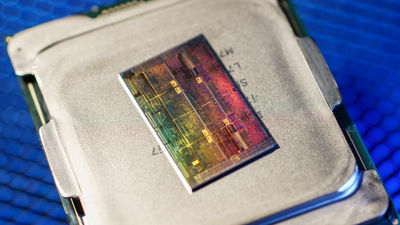

It is said that CMOS and MEMS are very expensive to create in the 7 nm process. Therefore, in the scaling of CMOS, the entire industry is moving in the direction of adopting “ System in a Package (SiP)” in which multiple LSI chips are sealed in one package without being integrated into one chip.

Optimal Integration of MEMS and CMOS Reveals Improved IC Performance-Semicon Portal

https://www.semiconportal.com/archive/editorial/technology/process/090928-memscmos.html

Zhang predicts that in the future there will be more semiconductor products that use SiP instead of System on a chip (SoC), which will create multiple circuits on a silicon chip to create one system with one chip. You are Chang said that by simply increasing integration density, development costs and semiconductor costs will rise to severe levels for most companies, combining technology focusing on power supply, power efficiency, and interconnect density. We have explained the need to build a solution.

Related Posts:

in Hardware, Posted by log1i_yk