AMDのGPU「RX 7900シリーズ」に採用された「RDNA 3アーキテクチャ」とは一体何なのか

2022年11月3日、AMDが次世代GPUアーキテクチャの「RDNA 3」の詳細を明らかにしました。RDNA 3では半導体上の個々のダイを個別に設計してひとまとめにする「チップレット」という技術を新たに採用しており、前世代と比較して大幅な性能向上を果たしています。このRDNA 3についてAMDから詳細を聞き出したテクノロジー系メディア・Tom's Hardwareのジャレッド・ウォルトン氏が、一体どんなものなのか解説しました。

AMD RDNA 3 GPU Architecture Deep Dive: The Ryzen Moment for GPUs | Tom's Hardware

https://www.tomshardware.com/news/amd-rdna-3-gpu-architecture-deep-dive-the-ryzen-moment-for-gpus

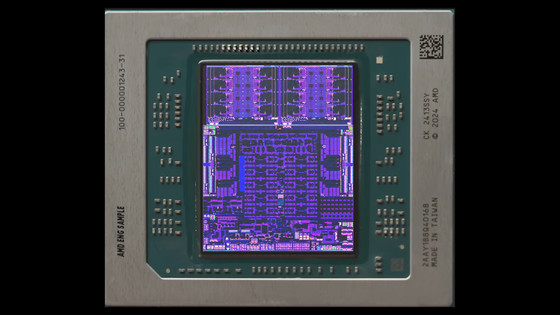

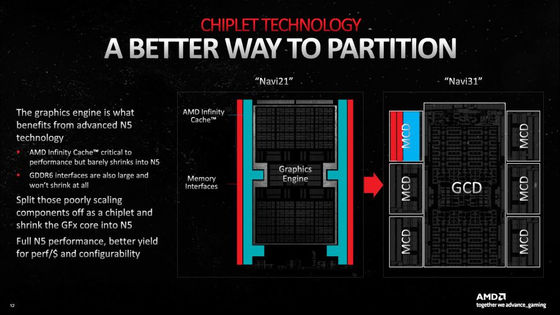

RDNA 3アーキテクチャを用いて作られるGPU「Navi 31」は、チップレットの採用により、5nmプロセスで製造されたGPUダイ(GCD)と6nmプロセスで製造されたキャッシュメモリ(MCD)が1つのパッケージにまとまっています。これによりメモリ帯域幅は最大5.3TB/sに向上し、処理性能は61TFLOPSに。消費電力当たりの性能は前世代の「RDNA 2」と比べて54%上昇しているなど、さまざまな面で性能が刷新されています。

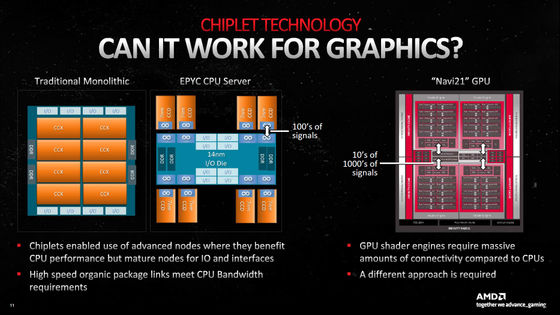

チップレットはAMDがCPUマイクロアーキテクチャの「Zen 2」以降で採用してきた設計で、Zen 2以降のCPUは入出力回路を搭載したダイ(IOD)を使ってシステムメモリと接続し、PCIe ExpressインターフェイスやUSBポート、Zen 4のグラフィックスやビデオ機能など、すべての機能を利用できるようにしています。さらにAMDはInfinity Fabricと呼ばれる設計を用い、CPUコアやキャッシュなどで構成されたCore Compute Die(CCD)とIODを接続しています。

設計上のポイントは、CPUコア上で動作するもののほとんどがL1・L2・L3の各種キャッシュ内に収まるということだとウォルトン氏は解説。Zen 4までの最新CPUではシステムRAM用の64-bitメモリチャネルは2つしかありません。

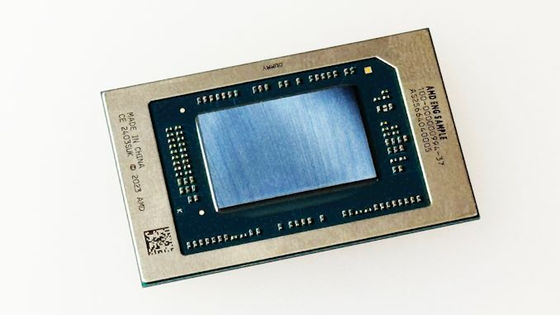

CCDは小さく、IODは125平方ミリメートル程度から416平方ミリメートルほど。直近では、Zen 4搭載「Ryzen 7000シリーズ」のIODはTSMCの5nmプロセス(N5)で製造された70平方ミリメートルのCCDを1~2個搭載したわずか122平方ミリメートルのIODを備えていますが、第4世代EPYCでは同じCCDを採用しながら396平方ミリメートルの比較的大きなIODとなったとのこと。

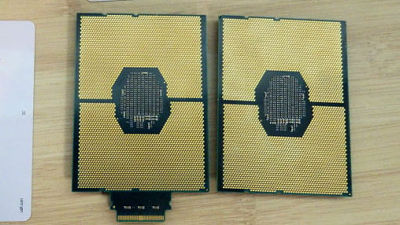

しかし、これらCPUで求められる要件とGPUで求められる要件は大きく異なります。GPUは大容量キャッシュや大量のメモリ帯域幅を必要とし、単純にCPUと比較すると、12チャネルDDR5構成の巨大な「EPYC 9654」でさえ、NVIDIA製GPUの「RTX 4090」の2分の1ほどの帯域幅しか実現することができません。

ウォルトン氏は「つまり、AMDはGPUチップレットを効果的に動作させるために、CPUとは異なるアプローチを採る必要があったのです」と指摘。AMDが編み出した解法は、CPUチップレットとほぼ逆に、メモリコントローラとキャッシュを複数の小さなダイに配置し、メインのコンピュート機能は中央のGCDチップレットに置くというものでした。

GCDには、すべてのCompute Units(CU:コア、スケジューラ、レジスタファイル、命令キャッシュ、テクスチャ・L1キャッシュ、エクスチャマッピングユニットなどを含むコンピューティングリソースの最小単位)と、ビデオコーデックハードウェア、ディスプレイインターフェイス、PCIe接続などのコア機能が搭載されています。Navi 31のGCDは最大96個のCUを搭載しており、ここで一般的なグラフィックス処理が行われるほか、上下のエッジにはInfinity Fabricがあり、そこからMCDに接続されています。

GCDはTSMCのN5ノードを使用し、300平方ミリメートルのダイに457億個のトランジスタを搭載しています。一方、MCDはTSMCの6nmプロセス(N6)ノードで製造され、わずか37平方ミリメートルのチップにそれぞれ20億5000万個のトランジスタを搭載。キャッシュと外部インターフェイスはGCDの1平方ミリメートルあたり平均1億5230万個のトランジスタを搭載している一方で、MCDの平均トランジスタ数は1平方ミリメートルあたり5540万個です。

ウォルトン氏は「GPUのチップレットアプローチの潜在的な懸念の1つは、Infinity Fabric回りのコンポーネントがどれだけの電力を必要とするかということです」と述べます。例えばZen CPUに使われるインターポーザーと呼ばれる基板は、GPUスケールに大きくするとかなりの電力を消費してしまうとのこと。そのため、AMDはNavi 31でインターフェイスの改良に取り組みました。

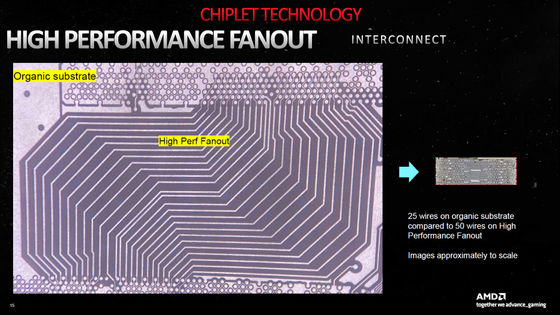

こうしてできあがったのが「ハイパフォーマンス・ファンアウト・インターコネクト」と呼ばれる設計で、以下画像の右側にあるNavi 31の部品に組み込まれています。左側にあるのはZen CPUで採用されている有機基板で、画像内の両者は、ほぼ現実と同じサイズ比で表示されています。左側には25本の配線が敷かれていますが、右側にはより小さい面積に50本が敷かれるという超高密度設計に進化しました。

これによりInfinity Fanout回りのすべてのコンポーネントを合わせて3.5TB/sの有効帯域幅を実現しながら、GPU全体の消費電力の5%未満で動くようになったそうです。

このほか、RDNA 3では浮動小数点演算のスループットが2倍になっていることに加えマトリクス(AI)のスループットも倍増し、マトリクス演算速度は全体で2.7倍に向上しています。キャッシュおよびシステムの他、部品間のインターフェイスはすべてアップグレードされており、例えばL0キャッシュはRDNA 2の2倍にあたる32KB、L1キャッシュも同じく2倍の256KB、L2キャッシュは1.5倍の6MBに増加しています。メイン処理装置とL1キャッシュのリンクは1.5倍になり、1クロックあたり6144バイトのスループットになったほか、同様にL1キャッシュとL2キャッシュの間のリンクも1.5倍広くなっているとのこと。

このようなRDNA 3を採用したRX 7900シリーズは、NVIDIAのRTX 4090には及ばないものの、RTX 4080には対抗できる可能性があるとのこと。「単純に計算すると32bit浮動小数点の1万2288シェーダーが2.5GHzで動作するのに対し、NVIDIAの1万6384シェーダーは2.52 GHzで動作するため、NVIDIAが61TFLOPS、AMDが83TFLOPSとなり、明らかに優位に立つことがわかります」とウォルトン氏は指摘。このほかメモリ帯域幅は少なくともかなり近いようで、この差はおそらくあまり問題にならないはずだと述べましたが、いずれにせよAMDのRX 7900シリーズが出るまで分からないとしました。

ウォルトン氏は「900ドル(約13万円)以上のグラフィックスカードに興味がない人にとって朗報なのは、2023年はRTX 4070と下位のAda Lovelaceパーツが登場し、AMDからRX 7800、7700、そして7600シリーズが提供される可能性が高いということです。これまで見聞きしてきたことから、将来のRTX 4070とRX 7800は、前世代のRTX 3090とRX 6950 XTと同様の性能を発揮し、より低価格で提供されることになりそうです」と述べました。

・関連記事

AMDが次世代GPU「Radeon RX 7900シリーズ」を発表、GeForce RTX 4000シリーズの対抗馬になり得るか - GIGAZINE

AMDが最大96コアの「第4世代EPYC」を発表、Zen 4アーキテクチャ採用でDDR5やPCIe 5をサポート - GIGAZINE

AMD製グラボがドライバ刷新で最大72%の性能向上を実現 - GIGAZINE

4K画質で120FPSをたたき出すNVIDIA DLSS3対応のGeForce RTX 4090搭載グラボ「TUF-RTX4090-24G-GAMING」でゲームしたり動画編集したりしてみた - GIGAZINE

・関連コンテンツ

in ハードウェア, Posted by log1p_kr

You can read the machine translated English article What exactly is the 'RDNA 3 architecture….