TSMCの次世代5nmプロセス&3nmプロセスは2022年に大量生産開始予定、2nmプロセスも研究開発中

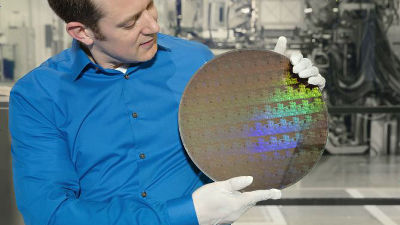

AppleやAMDに半導体を供給している世界最大の半導体ファウンドリ「TSMC」は、2020年6月から5nmプロセスによる半導体製品の製造を正式に開始しています。そんな中、TSMCのC・C・ウェイCEOが、次世代5nmプロセス&3nmプロセスの大量生産開始時期や2nmプロセスの研究開発状況について語っています。

Q1 2021 Taiwan Semiconductor Manufacturing Co Ltd Earnings Call on April 15, 2021 / 6:00AM - TSMC 1Q21 transcript.pdf

(PDFファイル)https://investor.tsmc.com/english/encrypt/files/encrypt_file/reports/2021-04/8b5438593d7b5d2181406a1b92d7304d6944c098/TSMC%201Q21%20transcript.pdf

TSMC Update: 2nm in Development, 3nm and 4nm on Track for 2022

https://www.anandtech.com/show/16639/tsmc-update-2nm-in-development-3nm-4nm-on-track-for-2022

◆5nmプロセス「N5」

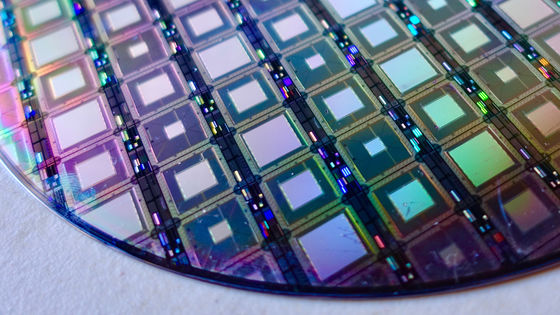

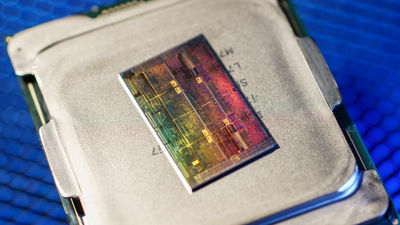

TSMCは、2020年6月に世界で初めて5nmプロセス「N5」での半導体製造を開始しました。ウェイCEOは「すでに、N5は量産から2年目に入り、当初の計画よりも優れた歩留まりを実現しています。2021年のN5の売上は、TSMCの半導体製造による収益の20%に達すると予想しています」と述べ、N5製造の順調さを強調しています。

技術系メディアのAnandTechによると、TSMCは生産した半導体の用途を開示していないとのこと。しかし、AnandTechは「N5はAppleのM1やApple A14 Bionicに使われていることが分かっています」と、N5がTSMC最大の顧客であるAppleが開発するSoCに用いられていると主張しています。

世界最大の半導体ファウンドリTSMCの顧客第2位にAMDが浮上か、1位はやはりあの企業 - GIGAZINE

また、ウェイCEOが「スマートフォンやHPCアプリケーションの需要の増加によって、N5の需要は今後数年間成長し続けると予想しています」と述べていることから、AnandTechは「ウェイCEOが述べたHPCアプリケーションには、CPU・GPU・FPGA・AIアクセラレータ・ゲーム機に搭載されたSoCなど、さまざまな種類の製品が含まれています。N5がどの製品に採用されいているかは分かりませんが、HPCアプリケーションにおけるN5の採用が進んでいることは重要な事実です」と指摘しています。

◆省電力版5nmプロセス「N5P」

香港に拠点を置く金融企業「China Renaissance Securities」のアナリストは、TSMCのN5が1平方mm当たり約1億7000万のトランジスタを備えていると推測しています。これに対してSamsungの5nmプロセスは1平方mm当たり約1億2500万~1億3000万、Intelの10nmプロセスでは1平方mm当たり約1億のトランジスタを備えているとのこと。AnandTechはTSMCのN5を「2021年4月時点で利用できる最も密度の高いテクノロジー」と評価しています。

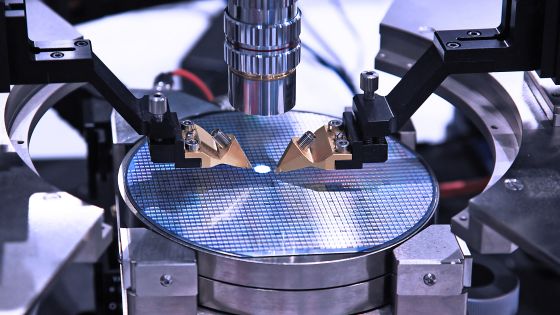

さらにAnandTechによると、TSMCは記事作成時点から数週間以内に省電力版5nmプロセス「N5P」による半導体製造を開始する予定とのこと。TSMCは「N5PはN5と同じ消費電力で動作周波数を最大5%増加させ、同じ動作周波数で消費電力を最大10%削減させることが可能」「半導体設計企業はN5からN5Pへの移行をスムーズに行える」と、N5Pの特徴を解説しています。

◆性能強化版5nmプロセス「N4」

TSMCは「N4」による半導体の製造を2021年下半期に開始し、2022年には大量生産を開始する予定です。

N4はN5と同様の設計ルールや製造機器を採用しつつ、N5よりもPPA(性能・消費電力・トランジスタ密度)を向上させ、製造段階でのEUVリソグラフィの使用をN5よりも拡張するとのこと。ウェイCEOは「N4は、N5と互換性のある設計ルールを用いています。N5で培った強力な技術基盤を活用して、5nmプロセスファミリーを拡張します」と述べています。

「ムーアの法則」の限界を回避できる期待の製造技術「EUVリソグラフィ」とは? - GIGAZINE

AnandTechは「TSMCは2022年にN4の大量生産を開始するまでに、EUVを用いた生産に3年、N5の生産に2年の経験を積むことになります。このため、N4の歩留まりは高く、安定したパフォーマンスが得られることが予想できます」と述べ、N4への期待を寄せています。

◆3nmプロセス「N3」

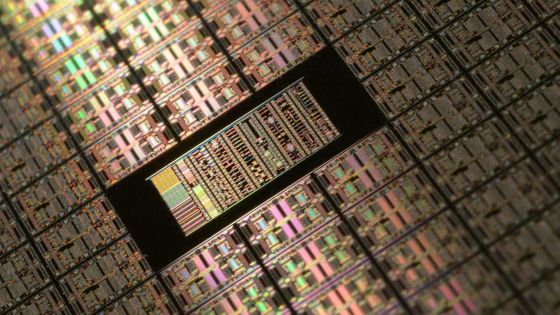

TSMCは、3nmプロセス「N3」による半導体の大量生産を2022年下半期に開始することを目標としています。

N3ではN5と比べて同一電力で10~15%の性能向上と同一パフォーマンスでの25~30%の消費電力削減が予定されています。また、N3ではEUVリソグラフィやDUVリソグラフィといった従来の技術が採用されており、新技術の開発が不要とのこと。AnandTechは「Samsungは3nmプロセス『3GAE』のために、独自の全周ゲートFET(GAAFET)である『MBCFET』を開発中です。これに対してTSMCのN3では新技術の開発が必要ないため、有意に競争を進められる可能性があります」と指摘しています。

ウェイCEOは「TSMCはN3の大量生産を2022年下半期に開始することを目指しています。私たちはN5とN3の両方に自信を持っています。両者はTSMCにとって長期的に利益をもたらすでしょう」と、N3への期待を語っています。

◆2nmプロセス

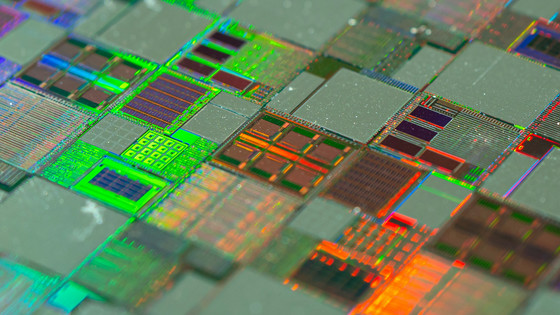

TSMCは、GAAFETを用いた2nmプロセスの研究開発を行っています。

TSMCが公開した2020年の(PDFリンク)年次報告書には「2nmプロセスの研究開発は順調に進んでいます」「TMCでは、2nmを超える微細化されたプロセスルールのために、メモリ技術や3Dトランジスタなどの分野に焦点を当てて研究開発を行っています」と記されています。

AnandTechは「TSMCは最近、3年間の研究開発費100億ドル(約1兆1000億円)に30億ドル(約3200億円)を追加投入しました。TSMCが研究開発を拡大していることは注目に値します」と述べています。

なお、以下がTSMCの各プロセスノードをまとめた表です。

プロセスノード | N7 | N7 | N7P | N7+ | N5 | N5P | N4 | N3 |

| 電力消費 | 60%削減 | 最大40%削減 | 10%削減 | 15%削減 | 30%削減 | 10%削減 | 削減 | 25~30%削減 |

| パフォーマンス | 30%向上 | ? | 7%向上 | 10%向上 | 15%向上 | 5%向上 | 向上 | 10~15%向上 |

| シリコンダイ面積 | 70%削減 | 37倍削減 | - | 約17%削減 | 45%削減 | - | - | 42%削減 |

| 大量生産開始時期 | 2019年第2四半期 | 2020年第2四半期 | 2021年 | 2022年 | 2022年下半期 |

・関連記事

TSMCが5nmプロセス・3nmプロセスの詳細を発表、3nmプロセスは2022年下半期に大量生産開始予定 - GIGAZINE

Appleのチップ製造を担当する世界最大の半導体製造ファウンドリ「TSMC」がアメリカ国内に工場を建設か - GIGAZINE

Intel・NVIDIA・TSMCの重役が「世界的な半導体不足は2021年中続く」と予測、最悪の予測は「2023年以降も続く」 - GIGAZINE

世界最大の半導体ファウンドリTSMCの顧客第2位にAMDが浮上か、1位はやはりあの企業 - GIGAZINE

世界最大の半導体製造ファウンドリにアメリカ政府が国内生産を要求、中国との対立が原因か - GIGAZINE

PlayStation 5とXbox Series Xが半導体大手のTSMCの製造ラインを圧迫しているという報告 - GIGAZINE

半導体の需要が供給を大きく上回ってファウンドリ市場がさらに成長するとの予想、半導体不足はしばらく続く可能性 - GIGAZINE

・関連コンテンツ

in ハードウェア, Posted by log1o_hf

You can read the machine translated English article TSMC's next-generation 5nm process &….