CPUのキャッシュメモリは何なのかについて専門家がわかりやすく解説

CPUのスペックを語る時、クロック周波数やコア/スレッド数のほかに、「CPUキャッシュメモリ」に言及されることがあります。このCPUキャッシュメモリとは何なのかについて、開発者のガブリエル・G・クンハ氏が解説しています。

Pikuma: Exploring How Cache Memory Really Works

https://pikuma.com/blog/understanding-computer-cache

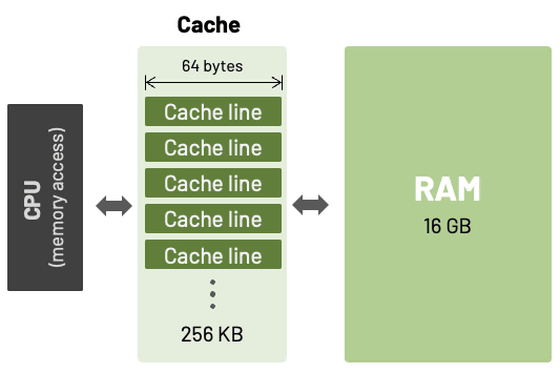

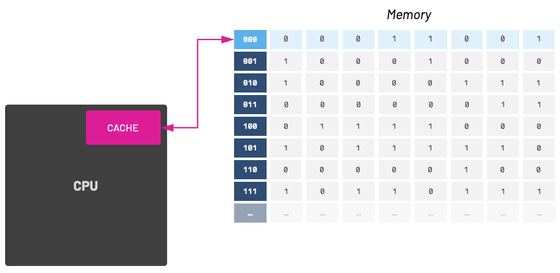

キャッシュメモリは、CPUとメインメモリ(RAM)の間に位置し、両者の速度差を埋めるために存在します。CPUの処理速度がRAMのアクセス速度を大幅に上回るようになったため、頻繁に使用するデータを高速なキャッシュに一時的に保存することで、CPUがデータ待ちで処理を中断する時間を減らすことができます。

RAMのデータは「キャッシュライン」と呼ばれるブロック単位でキャッシュに読み込まれます。キャッシュラインのサイズはプロセッサのアーキテクチャによって異なり、一般的に32バイト、64バイト、128バイトです。

CPUが必要とするデータがキャッシュ内に存在する場合を「キャッシュヒット」と呼び、高速なアクセスが可能。逆に、データがキャッシュ内に存在せず、RAMまで読みに行く必要がある場合を「キャッシュミス」と呼び、パフォーマンスの低下につながります。したがって、プログラマーはキャッシュヒット率を高め、キャッシュミスを減らすことを意識する必要があります。

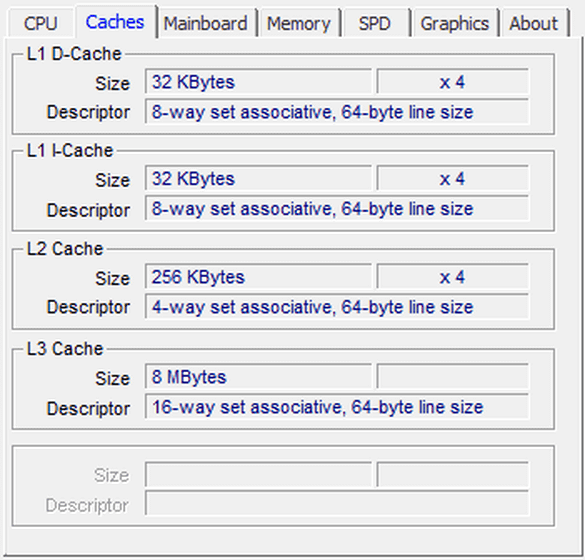

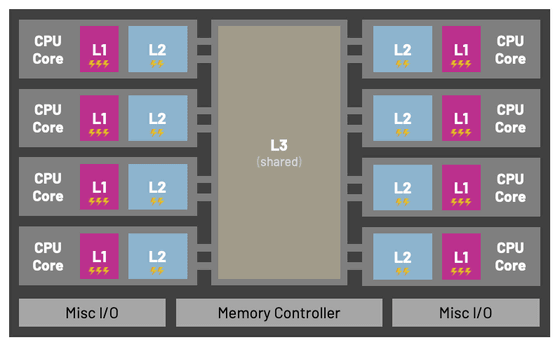

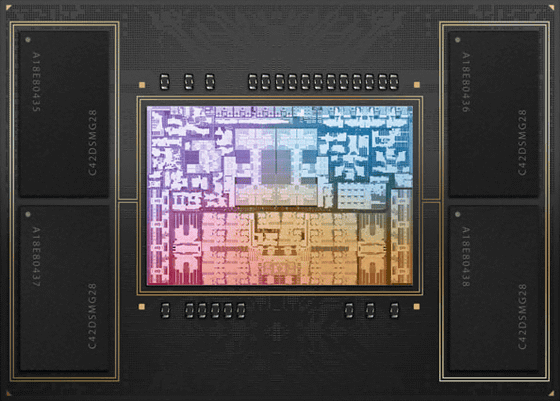

現代のCPUキャッシュは、通常L1、L2、L3といった複数の階層で構成されています。

・L1キャッシュ

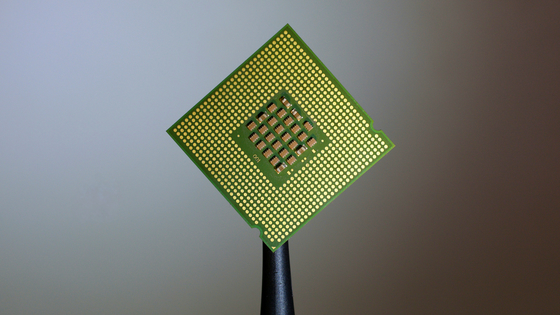

CPUコアに最も近く高速ですが、容量は数十KBとかなり小さくなります。L1キャッシュは、プログラムが処理するデータ用のデータキャッシュ(d-cache)と、アセンブリコードなどの命令を保存する命令キャッシュ(i-cache)に分離されていることが多くあります。例えば、1993年に登場したIntel Pentiumは、データキャッシュ用と命令キャッシュ用にそれぞれ8KBのL1キャッシュメモリが搭載されていました。

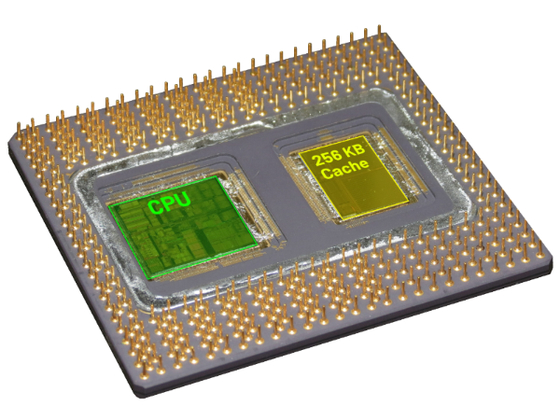

・L2キャッシュ

L2キャッシュは L1キャッシュよりも低速ですが、容量は数百KBと大きくなります。1995年に登場したPentium ProはIntelのx86プロセッサとして初めてL2キャッシュを内蔵したモデルで、その容量は256KBあるいは512KBでした。

・L3キャッシュ

L3キャッシュは最も低速ですが、容量が数MBと最も大きいキャッシュメモリで、複数のCPUコアで共有されることが一般的です。

データキャッシュはデータを保存するため、読み込みと書き込みの両方に対応しますが、命令キャッシュは実行中に書き換えられることがほとんどないため、基本的に読み取り専用として機能します。データキャッシュと命令キャッシュはアクセスの性質が異なるため、役割を分けることでより効率的なキャッシュシステムを構築できます。

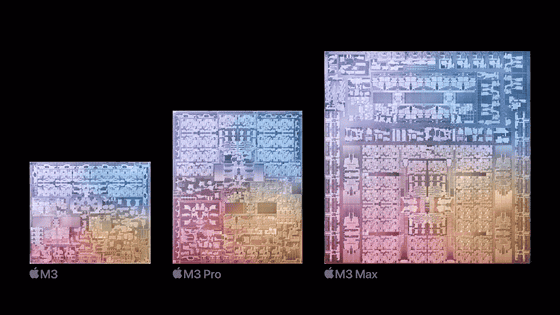

現代のアーキテクチャでは、命令キャッシュとデータキャッシュが別々に搭載されています。ほとんどのARM CPUはL1内に命令キャッシュとデータキャッシュを別々に搭載していますが、L2内ではこれらが統合されています。

例えば、AppleシリコンのM1とM2でも、命令キャッシュとデータキャッシュは別々になっています。M2のCPUには高性能コアと高効率コアの2種類が搭載されており、高性能コアは192KBのL1命令キャッシュと128KBのL1データキャッシュ、16MBのL2キャッシュを搭載しています。一方、高効率コアは192KBのL1命令キャッシュと64KBのL1データキャッシュ、4MBのL2キャッシュを搭載しています。

キャッシュは、一度読み込んだデータの周辺データもまとめて読み込む性質があります。そのため、処理で使うデータをメモリ上でなるべく近くに配置することが重要です。

例えば、C言語の2次元配列を処理する場合、Cの配列は行優先でメモリに格納されるため、内側のループで列を、外側のループで行を処理する方がキャッシュ効率は格段に高くなります。これは、メモリ上の連続したデータに順次アクセスすることになり、キャッシュヒット率が向上するためです。

int sum_matrix_rows(int mat[M][N]) {

int sum = 0;

for (int i = 0; i < M; i++) {

for (int j = 0; j < N; j++) {

sum += mat[i][j];

}

}

return sum;

}

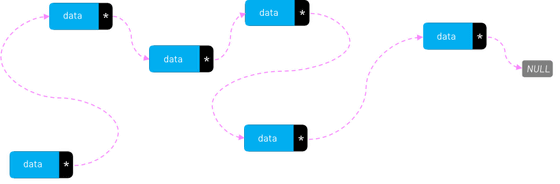

逆に、各要素がメモリ上に散らばりがちなリンクリストは、キャッシュの観点からは効率の悪いデータ構造と言えます。

クンハ氏は「コンピュータのメモリがどのように機能し、CPUとどのように連携して動作するかについての新しい知識を活用して、キャッシュ操作についてさらに深く理解を深めていただければ幸いです」と述べています。

・関連記事

CPU使用率が増加するとパフォーマンスがどのように低下するかをGitHubのパフォーマンスエンジニアリングチームが解説 - GIGAZINE

17歳の学生が独学で「どのようにCPUがプログラムを動かすのか」を調査し詳細に解説するページを作成 - GIGAZINE

第3世代Ryzenで採用されるAMDの次世代アーキテクチャ「Zen 2」についてWikiChipが解説 - GIGAZINE

PlayStation 5 Proに搭載されたAMD製GPUの仕様を解説する公式動画が登場、「PS5 Proの開発は2020年に始まった」「世界初のレイトレーシング技術を搭載」など興味深い情報多数 - GIGAZINE

DRAMが世界をどう変えたかを半導体大手のMicronが解説 - GIGAZINE

・関連コンテンツ

in ハードウェア, Posted by log1i_yk

You can read the machine translated English article An expert explains in an easy-to-underst….