Intelの見直されたプロセスルールと新たなロードマップについてIntel技術幹部が語る

Intelの技術開発担当上級ゼネラルマネージャーを務めるアン・ケレハー氏が、半導体関連のニュースサイトであるSemiconductor Engineeringによるインタビューで、Intelが見据える今後のロードマップについて語っています。

Inside Intel's Ambitious Roadmap

https://semiengineering.com/inside-intels-ambitious-roadmap/

Semiconductor Engineering(以下、SE):

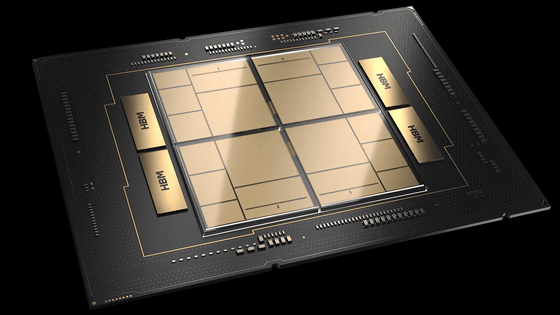

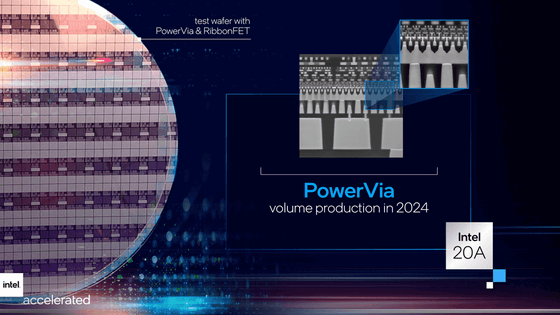

Intelは2021年7月に2025年までのロードマップを公開しました。従来のプロセスノードも「Intel 7」「Intel 4」「Intel 3」と改名し、さらに「Intel 3」を超える「Intel 20A」を発表しました。

IntelがQualcommと提携し新チップを製造すると発表、2025年までのロードマップも公開 - GIGAZINE

このIntel 20Aでは電界効果トランジスタ(FET)の新アーキテクチャである「RibbonFET」を実装する予定とのことですが、RibbonFETとはそもそも何ですか?

アン・ケレハー氏(以下、ケレハー氏):

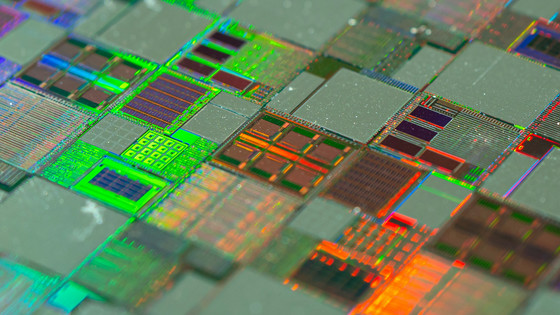

RibbonFETはIntelでの呼び方で、業界では「ゲート・オール・アラウンド構造」と呼ばれているもので、FinFETを超える次世代のトランジスタアーキテクチャです。Intel 3まではFinFETの改良が行われていきますが、Intel 20Aでは他社とほぼ同等のプロセスノードでRibbonFETを採用する予定です。

SE:

FinFETについては、Intelはかなり進んでいましたね。RibbonFETは最先端のノードであり、業界を再び進歩させます。現在のEUVリソグラフィーを使ってRibbonFETを実現できますか?

ケレハー氏:

2024年に計画されているIntel 20Aでは、露光装置の開口数(NA)が0.33という既存のEUVリソグラフィーを使っています。2025年以降のプロセスでは次世代高NA EUVリソグラフィーを使う方向でASMLとすでに提携済みです。次世代高NA EUVリソグラフィーによって、はるかに小さな形状、はるかに小さなピッチに移動でき、ダブルパターニング技術を使い続けることも可能になります。

私たちが高NA EUVリソグラフィーに興味を持ったのは数年前で、2018年頃からASMLと「次は何をするのか」という話をしていました。つまり、業界全体で目指す必要がある目標です。そこで、2025年に向けてIntelが打ち立てた目標が、次世代高NA EUVリソグラフィーの採用です。EUVリソグラフィーは私たちの10nmプロセス、すなわちIntel 7では導入されていませんでしたが、Intel 4では導入されています。私たちは今後もEUVリソグラフィーの最先端を維持したいと考えています。

SE:

IntelはIntel 3までFinFETを採用し、Intel 20A以降でRibbonFET、すなわちゲート・オール・アラウンド構造トランジスタを採用します。一方、競合他社であるSamsungは3nmプロセスでゲート・オール・アラウンド構造トランジスタを採用しました。なぜIntelはIntel 3でRibbonFETを採用しなかったのですか?

ケレハー氏:

私たちは、本来の最適化という観点から、FinFETのロードマップをさらに改善できることを知っていました。では、まったく異なるアーキテクチャに移行する前に、これらのメリットを活用してはどうでしょうか。肝心なのは「いつやるのが適切なのか」ということです。私たちは、RibbonFETが基本的に既存のFinFETからより多くのものを提供できるという信念に基づいて移行します。他の業界がどのようにゲート・オール・アラウンド構造を導入するかは、いつかわかることでしょう。

SE:

ゲート・オール・アラウンド構造トランジスタについては、以前から複数の企業が取り組んでいます。この技術にはどのような課題があるのでしょうか?

ケレハー氏:

ここ数年で、EUVリソグラフィー技術は大きく成熟し、本格的に採用されるようになりました。これまでEUVリソグラフィーがすべてのレイヤーに対応できるのかという疑問がありましたが、EUVリソグラフィーの印刷工程も明らかに簡単になりました。ゲート・オール・アラウンド構造を実現する上で、EUVリソグラフィーは重要な役割を果たします。これらの問題に加えて、スタックの高さや基板の絶縁分離(アイソレーション)をどうするかについても考えなければなりません。すべて対処すべき課題ですが、私たちはこれらすべてを解決し、欠点を減らしながら期限内に納品するための道筋を把握しています。

SE:

そもそもIntelがプロセスノードの名前を変更したのはなぜですか?

ケレハー氏:

要するに半導体業界全体でノードの呼称にズレが生じていたのです。Googleで検索すると、「Intelの10nmは他のファウンドリでは7nmに相当する」という説明が出てきます。私たちはお客様に分かりやすくすることを考えなければなりませんでした。ノードの命名戦略を変更してから、ようやくお客様がプロセスノードとその名称を見て、より良い判断ができるようになりました。

私たちは3月にIDM 2.0のビジョンを発表し、そこから半年間、多くの時間を費やして非常に詳細なロードマップを作成してきました。

Intelが2兆円超を投じてファウンドリサービスの拡充を目指す「IDM 2.0」を発表、「Apple Siliconの製造を目論んでいる」との指摘も - GIGAZINE

新しいロードマップでは、1W(ワット)あたりの性能で他社と並び、1Wあたりの性能でリーダーシップを発揮できるようにするための方法が示されています。そのような状況の中で、私たちは今こそ名前を変える時だと考えました。私たちはノードの名前を説明するよりも、自分たちがやっているものに集中することに時間を費やしているのです。

SE:

インテルの7nmプロセス技術に遅れが生じているといわれていましたが、近況はどうなっていますか?

ケレハー氏:

発表した通り、当時7nmプロセスと呼ばれていたものは、現在はIntel 4という名前になりました。名前を変えた時点で、プロセス全体の開発と欠陥密度を踏まえて一度マイルストーンをリセットしました。それからプロセスフローを効率化するために、基本的に古いプロセスフローと新しいプロセスフローを同時並行で進めながら、EUVリソグラフィーの採用を増やしました。その結果、2021年に入ってから元のプロセスフローから新しいプロセスフローに切り替えることができました。この新しいプロセスフローは非常にうまくいっています。

私たちはこの9ヵ月間でマイルストーンを達成し、私たちが行っている作業が成果を上げていると確信できました。他にも1Wあたりのパフォーマンスで業界を先導するためのロードマップをどのようにまとめるかについて話しました。まずかなりの数のプロジェクトを企画し、実現するための研究開発と資本を投入しています。そして、Intelの技術開発グループには世界トップクラスのエンジニアがいます。以前からそうでしたし、今もそうです。しかし、私たちの仕事のやり方は変化しつつあります。可能な限り、そして意味がある限り、私たちは業界標準を採用します。

SE:

Intelは、4年間で5つのノードを計画しており、競合他社と肩を並べた上で、業界のリーダーとしての地位を目指しています。これは、これまでの「18~24カ月ごとに新しいプロセスノードを発表する」という法則を覆すものですよね?

ケレハー氏:

私たちは2021年後半にIntel 7の製品をリリースします。そして、Intel 4は2022年後半に製品化され、2023年に市場に出回ります。Intel 3の登場は2023年後半です。2024年にIntel 20Aが続き、その後にIntel 18Aが登場します。次のノードに移行した時の1Wあたりのパフォーマンスはどれも大きく向上します。しかし、競合他社に追いつきたい、あるいはその先に進みたいのであれば、チップはより速く動く必要があります。今回お話した方法論は、それを可能にするためのものです。私たちはこれを実現するために、非常に堅実なロードマップを描いているのです。

・関連記事

世界中の半導体製造業者が頼る露光装置メーカー「ASML」はどんな会社なのか - GIGAZINE

Intelがゲーム高画質化技術「XeSS」や次世代プロセッサ「Alder Lake」の詳細を発表 - GIGAZINE

IntelがQualcommと提携し新チップを製造すると発表、2025年までのロードマップも公開 - GIGAZINE

Intelに「Sandy Bridge」「Skylake」を生んだベテランアーキテクトのシュロミット・ワイス氏が復帰 - GIGAZINE

・関連コンテンツ

in ハードウェア, Posted by log1i_yk

You can read the machine translated English article Intel technical executives talk about In….