TSMCは5nmプロセスの先行生産を2019年4月にも行う予定

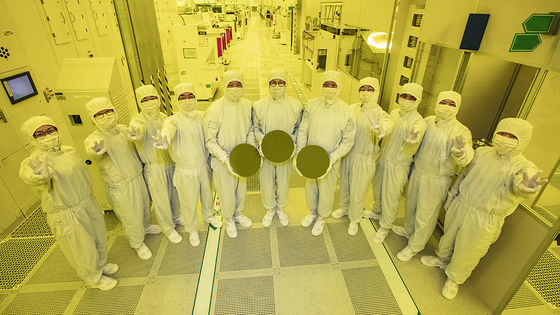

半導体ファウンドリ(ファブ)のTSMCが、早ければ2019年4月にも5nmプロセスでのリスクプロダクションを行うことを明らかにしました。

TSMC to Start 5nm Production in April - EE Times Asia

https://www.eetasia.com/news/article/18100502-tsmc-to-start-5nm-production-in-april

TSMC: First 7nm EUV Chips Taped Out, 5nm Risk Production in Q2 2019

https://www.anandtech.com/show/13445/tsmc-first-7nm-euv-chips-taped-out-5nm-risk-in-q2

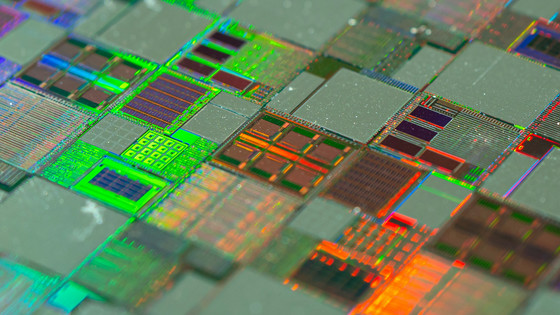

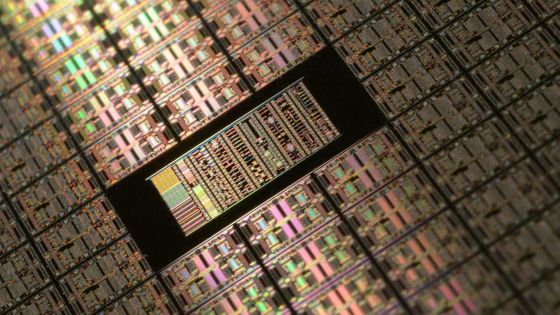

TSMCは極紫外線リソグラフィー(EUV)に関して重要な発表を2つ行いました。その1つは、第2世代の7nmプロセス(N7+)の製造が始まったというもの。TSMCはすでに2018年4月に第1世代の7nmプロセス(N7)での半導体大量生産を始めていましたが、新たにN7+で最初のカスタマー向けチップのテープアウトを行いました。N7+はN7比でトランジスタ密度は20%アップしており、消費電力は8%ダウンし周波数は6~12%高まると期待されています。

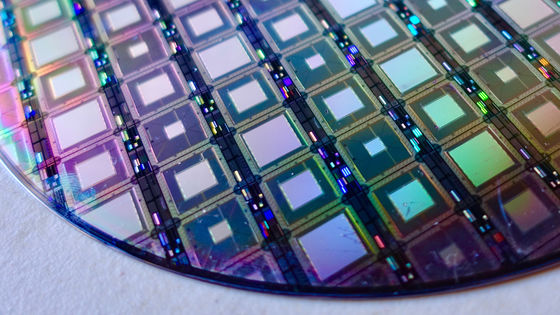

もう1つの重大発表として、TSMCは5nmプロセス(N5)でのRisk Production(リスクプロダクション)を早ければ2019年4月にも行う計画だと明言しました。「リスクプロダクション」とは、特定の顧客からのチップ生産の依頼を受けることなく半導体ファブが独自に先行試験として行う生産です。そもそも需要があるのかも手探りな段階で、半導体ファブが先行投資によりリスクを負うためこう呼ばれています。

N7+はあくまでN7の改良版プロセスであり性能面での飛躍的な進歩は望めません。これに対して、微細化が進むN5では、最大14層のEUVが用いられ半導体の密度が大幅に改善する予定です。具体的には現在主流のN7世代の半導体チップと比べて、N5ではトランジスタ密度が1.8倍になり、半導体メーカーは設計面積を約45%縮小できる予定で、消費電力は20%ダウンし、周波数は15%アップできると見込まれています。

TSMCは2019年4月にN5のリスクプロダクションを開始する計画ですが、一般的にリスクプロダクションから製品化に向けた大量生産までにかかる期間は約1年なので、2020年Q2(4月から6月)に、5nmプロセスを採用した半導体チップが市場に投入されることになりそうです。TSMCに半導体製造を委託しているAppleの場合、2020年モデルのiPhoneには5nmプロセスの「A14(仮称)」チップが採用される可能性が高そうです。

EUV技術の導入が不可欠になっている半導体ファブ業界では、ファブの立ち上げにかかる費用がうなぎ上りという状況になっています。そのため、ライバルのGlobalfoundriesが7nmプロセスでの生産を中止すると発表するなど、開発競争は熾烈になっています。2020年まで半導体業界が好調を維持できるかどうか不透明な中、TSMCは巨額の先行投資というリスクを取りつつ、ライバルのSamsungやIntelを突き放す構えです。

・関連記事

「ムーアの法則はもう限界」とiPhoneにチップを提供する半導体大手TSMCの会長が発言 - GIGAZINE

7nmプロセスのチップを採用するスマホメーカーはAppleとSamsungだけになる可能性アリ - GIGAZINE

Samsungが7nmプロセス製造技術を早くも完成、前倒しの量産でスマホの速度&バッテリー持ちの向上に期待 - GIGAZINE

IBMが5nmプロセスのチップ製造に成功、世界初のEUVリソグラフィ実用化へ - GIGAZINE

半導体ファブGlobalFoundriesが7nmプロセスを全部中止へ方針転換 - GIGAZINE

「ムーアの法則」の終焉は何を意味するのか? - GIGAZINE

・関連コンテンツ

in ハードウェア, Posted by darkhorse_log

You can read the machine translated English article TSMC plans to pre-produce 5nm process in….