IBMが5nmプロセスのチップ製造に成功、世界初のEUVリソグラフィ実用化へ

「半導体の集積密度は18カ月で2倍になる」という経験則の「ムーアの法則」が成り立たなくなっているとささやかれている半導体製造で、IBMが世界初の5nmプロセスのチップの開発に成功したと明らかにしました。5nmプロセスチップによって、省電力性能が劇的に向上すると期待されています。

IBM unveils world’s first 5nm chip | Ars Technica UK

https://arstechnica.co.uk/gadgets/2017/06/ibm-5nm-chip/

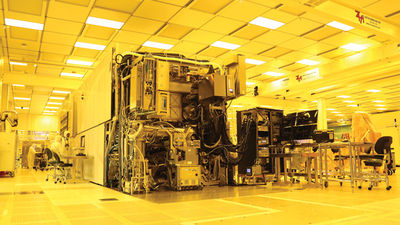

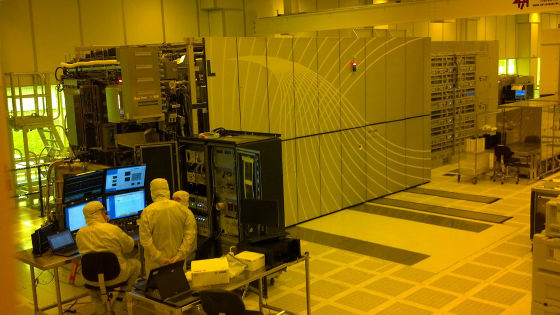

IBMが開発に成功したのは、回路幅が5nmのプロセスルールで、世界初の「(Extreme ultraviolet lithography(EUV:極端紫外線リソグラフィ)」技術を用いて製造したもの。IBMには、半導体製造のGlobalFoundriesとSamsungが技術協力しています。

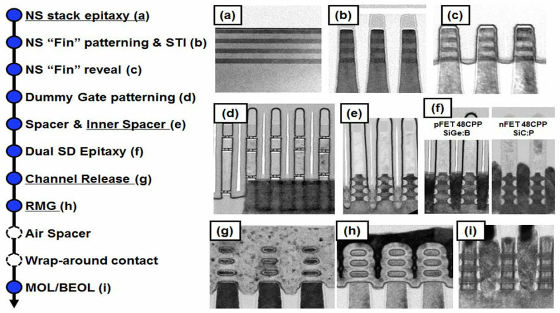

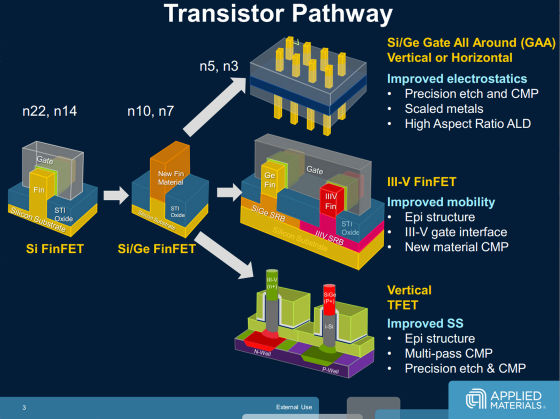

5nmプロセスチップでは極端紫外線リソグラフィだけでなく、「gate-all-around(GAA)」を世界で初めて実用化した例だとのこと。GAAはナノワイヤをゲート電極で取り囲むことで電流を制御しやすくするのが狙いで、高速スイッチングが可能で、従来の垂直方向に半導体回路を積層していくFinFETの欠点を補うものです。以下の(a)から(i)が、5nmプロセスのGAAFETの製造工程を示したもの。GAAFETの製造では、シリコン(Si)とシリコンゲルマニウム(SiGe)を交互に積み重ね、「原子層エッチング」と呼ばれる工法でSiGeを除去して隙間を残し、その隙間を高誘電率膜(high-k材料)で埋めて作ります。

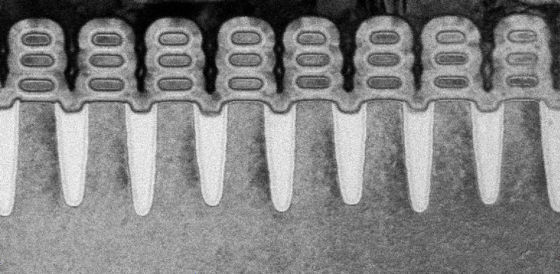

完成した5nmプロセスのGAAFETの断面の拡大図がこれ。各トランジスタは垂直方向に3層構造で積層化されたナノシートから成り、その回りをゲート材料が取り囲むように配置されています。

なお、GAAFETの製造でEUVを用いる手法では、最高でプロセスルールは3nmまで進化できるとのこと。

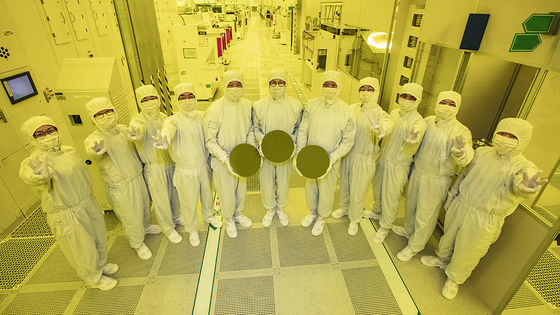

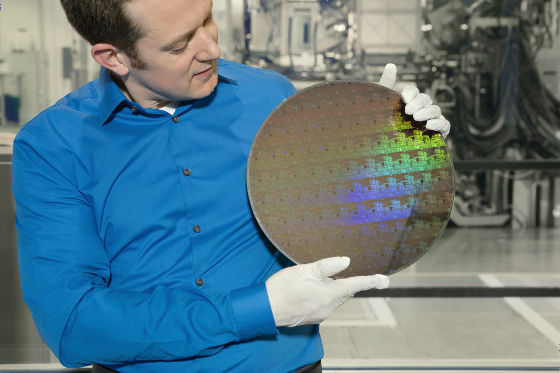

これが世界初の5nmプロセスで製造された半導体チップのウエハー。IBM研究所の半導体製造責任者のヒューミング・ブー氏は、「EUVリソグラフィがフロントエンドのパターニングに初めて使用された例です」と述べています。既存の液浸リソグラフィ装置の波長が193nmなのに対してEUVでは13.5nmという短い波長を使うことで、パターニングの工程数を減らすことができるそうです。

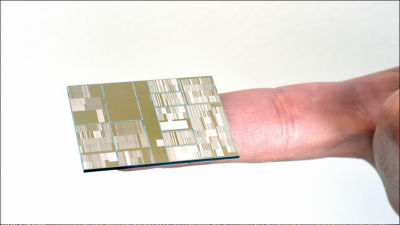

実用化まで約10年間かかったEUVによる半導体製造技術は、数カ月後に市場に投入される予定だとのこと。IBMによると、5nmプロセスチップは現在市販されている10nmプロセスチップに比べて、同じ電力で40%の性能向上、75%の消費電力量の削減が実現しているそうです。

半導体製造では、製造コストを下げて信頼性を高めるために、既存製品の製造技術ととオーバーラップする形で新技術が導入されることが多いため、即座に5nmプロセスのGAAFET製品が誕生するとは限りません。そのため、5nmプロセスのGAAFETではなく、既存のSiGeで製造されるFinFETが7nmプロセス や5nmプロセスに微細化が進む可能性があるとArs Technica UKは指摘しています。

・関連記事

IBMが10nm世代を飛び越えて7nmプロセスの半導体チップ試作に成功しムーアの法則が堅持される見込み - GIGAZINE

「ムーアの法則」の終焉は何を意味するのか? - GIGAZINE

「ムーアの法則」の限界を回避できる期待の製造技術「EUVリソグラフィ」とは? - GIGAZINE

ムーアの法則に黄色信号点滅、Intelの10nmプロセス移行の遅れが確実に - GIGAZINE

IBMが人間の脳と同じ構造を持つプロセッサーの開発に成功 - GIGAZINE

・関連コンテンツ

in ハードウェア, Posted by darkhorse_log

You can read the machine translated English article IBM succeeded in manufacturing 5-nm proc….