Intelが「ムーアの法則」を再出発させる裏面電力供給技術「PowerVia」のテストに成功、Intelは「ライバルの2年先を行く」「ピザ作りをやめる」とアピール

IntelがCPUのトランジスタ密度向上に寄与する裏面電力供給技術「PowerVia」のテスト実装に成功したことを報告しました。PowerViaの開発によりIntelが掲げる「2030年までに1パッケージに1兆個のトランジスタを詰め込む」という目標の実現に近付いたとのことです。

With PowerVia, Intel Achieves a Chipmaking Breakthrough

https://www.intel.com/content/www/us/en/newsroom/news/powervia-intel-achieves-chipmaking-breakthrough.html

PowerVia Test Shows Industry-Leading Performance

https://www.intel.com/content/www/us/en/newsroom/news/powervia-test-shows-industry-leading-performance.html

What is PowerVia?

— Intel News (@intelnews) June 5, 2023

Read how Intel developed and proved the world's first backside power solution, taking a major step forward in chipmaking: https://t.co/aWKT8OL8iL pic.twitter.com/8mtpq6REUi

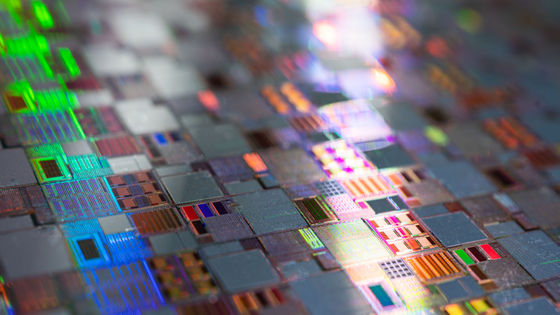

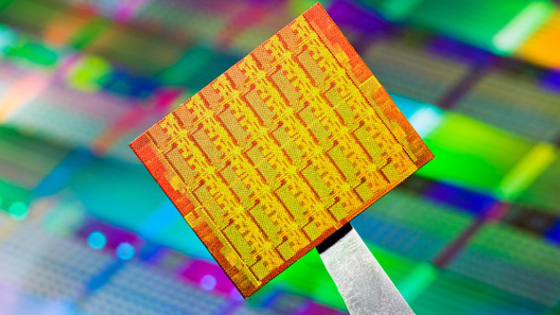

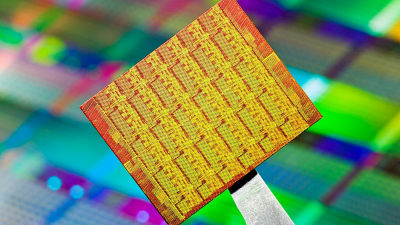

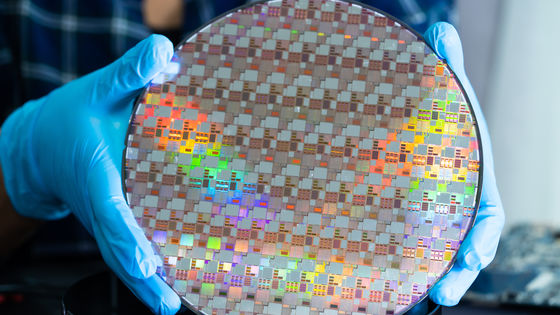

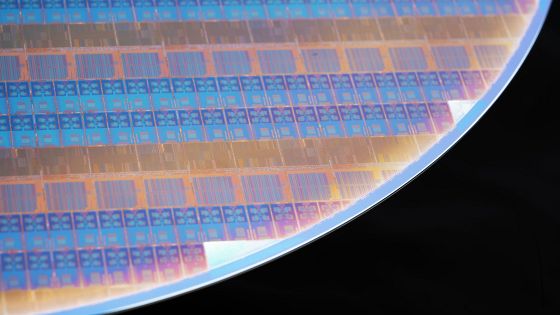

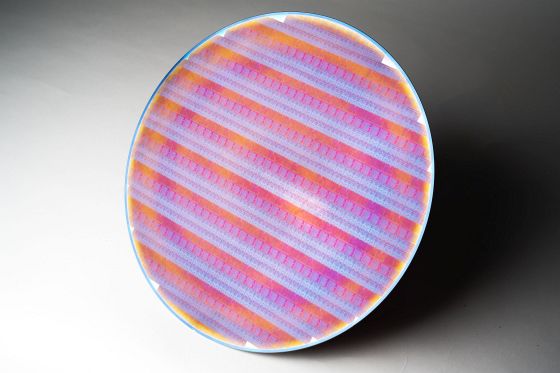

記事作成時点で流通しているCPUのトランジスタは「下から順にトランジスタや配線を積み上げる」というピザ作りに似た方式で生産されています。現行のCPUではピザ作り的な製法でも問題が生じることはありませんでしたが、チップの微細化が進んだことで電力供給システムが処理システムのボトルネックになる事態が発生しつつありました。

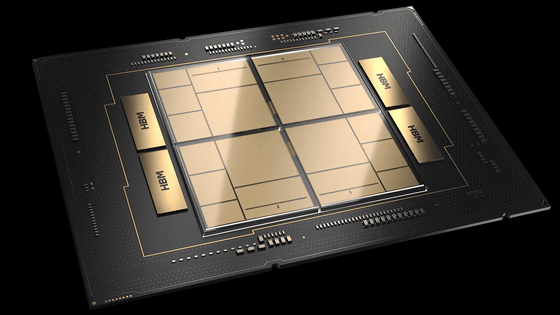

CPUのボトルネックを解消するために、チップメーカー各社は電力供給システムをチップの裏側に搭載する「裏面電力供給技術」の開発を進めています。Intelも裏面電力供給技術「PowerVia」の開発を進めており、2023年6月5日には開発中のCPU「Meteor Lake」のEfficient Core(Eコア)にPowerVia技術を投入するテストの成功が発表されました。IntelはPowerViaの開発について、従来のCPUの構造を引き合いに出して「ピザ作りをやめる」と表現しています。

PowerViaを用いたCPUでは電力効率が上昇し、トランジスタ密度も向上するとのこと。IntelはPowerViaによるトランジスタ密度向上について「ムーアの法則の約束がふたたび実現しました」「Intelが2024年にPowerViaを製品に導入すれば、競合他社はIntelに対して『2年の遅れ』を喫することになります」と述べています。

なお、Intelは2023年6月11日~16日に京都で開催される「VLSI Symposium」でPowerViaの詳細を発表する予定とのことです。

VLSI Symposium | Symposium on VLSI Technology and Circuits

https://www.vlsisymposium.org/

・関連記事

Intelが業界最先端を狙うプロセスルール「Intel 20A」「Intel 18A」の開発を完了 - GIGAZINE

Intelが考える「ムーアの法則」の次の波とは? - GIGAZINE

IntelがQualcommと提携し新チップを製造すると発表、2025年までのロードマップも公開 - GIGAZINE

Intelが毎秒200京回計算するスパコンを使って1兆パラメーターのジェネレーティブAIを開発中 - GIGAZINE

Intelが32ビット対応を切り捨てた新アーキテクチャ「x86S」を開発中 - GIGAZINE

Intelがサーバー事業から撤退、データセンター部門を台湾のMiTACに売却へ - GIGAZINE

・関連コンテンツ

in ハードウェア, Posted by log1o_hf

You can read the machine translated English article Intel succeeds in testing the backside p….