Intelがムーアの法則を加速させるための計画を発表、配線密度10倍以上&ロジックスケーリング最大50%向上を目指す

Intel創設者のひとりであるゴードン・ムーアが提唱した「半導体の集積密度は18~24カ月で倍増し、チップの性能が倍になってもさらなる小型化が進む」という経験則・ムーアの法則に伴い進化を続けてきた半導体ですが、近年はムーアの法則通りの進化を遂げられずにおり、法則に限界が訪れつつあると報じられてきました。そんなムーアの法則に則った半導体の進化を実現するため、IntelがIEEE主催のIEDM 2021の中で、最新技術を発表しています。

Intel Breakthroughs Propel Moore’s Law Beyond 2025

https://www.intel.com/content/www/us/en/newsroom/news/intel-components-research-looks-beyond-2025.html

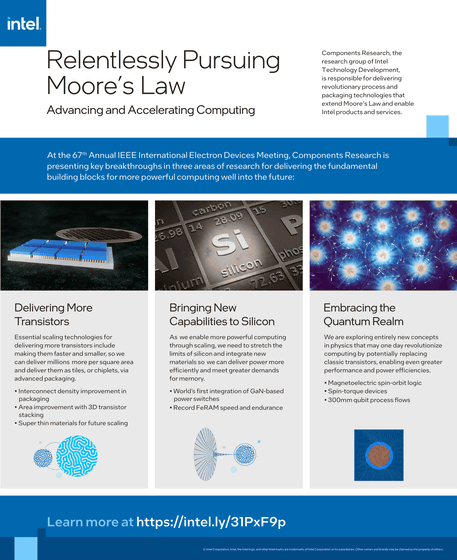

Intelのコンポーネント研究グループが、「電力とメモリを増やすための新しいシリコン機能」や「コンピューティング方法に革命を起こすための物理学における新しい概念の探求」を行うために、以下の3つの主要分野における革新に取り組んでいると発表しました。Intelは3つの主要分野における革新により、「2025年以降もムーアの法則通りの半導体の進化が可能になる」と主張しています。

Intelが明かした3つの主要分野における革新は以下の通りです。

◆1:Intelは将来の製品提供でより多くのトランジスターを提供するために不可欠なスケーリング技術の研究を推進中。

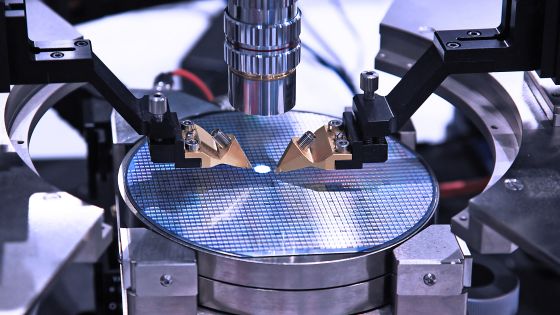

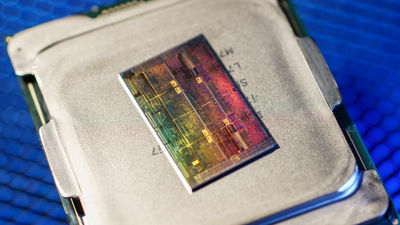

Intelの研究者は、ハイブリッド接合における設計・手順・組み立てに関するソリューションを改善し、パッケージングにおける相互接続密度を10倍以上に向上させることを想定しています。Intelは3Dスタッキング(三次元積層)における相互接続密度の高さを実現するため、サブ10ミクロンのバンプピッチを実現するための次世代3Dパッケージング技術「Foveros Direct」を発表。Intelはエコシステムが高度なパッケージングのメリットを享受できるようにするために、ハイブリッドボンディングチップレットエコシステムを実現し、新しい業界標準とテスト手順の確立を求めているとしています。

Foveros Direct: Advanced Packaging Technology to Continue Moore’s Law - YouTube

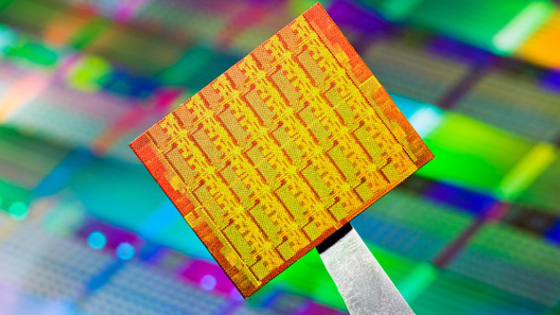

さらに、IntelはGAA構造を持つ電界効果トランジスタ(FET)である「RibbonFET」を超え、ムーアの法則の継続的な進化を実現するためのMOSFETの構想も進めています。Intelは最大30~50%のロジックスケーリング改善を可能にするため、複数のCMOSトランジスタをスタックするアプローチでFinFET後の時代に対応していくとしました。これにより、1平方ミリメートルあたりにより多くのトランジスタを取り付けることが可能になります。

加えて、Intelはムーアの法則がオングストローム時代に進む道を切り拓いており、わずが数原子分の厚みしかない新しい材料の採用を目指しています。これが実現すれば、従来のシリコンチャネルにおける制限を克服し、ダイ領域あたり数百万のトランジスタを敷き詰めることが可能になります。

◆2:Intelはシリコンに新しい機能を追加する予定。

Intelはより効率的な電力技術として、300mmウェハー上のCMOSシリコンとGaNベースの電力スイッチの世界初の統合を目指して研究を進めています。これが実現すればCPUへの低損失・高速電力供給が可能となり、さらにマザーボード上のスペースを削減することもできます。

さらに、ゲームから人工知能(AI)にいたるまでますます複雑になっているコンピューティングアプリケーションに提供するため、次世代組み込みDRAMテクノロジーに対応する新しい強誘電体材料を使用した業界をリードする低遅延の読み取り・書き込み機能の実現も目指しています。

◆3:Intelはシリコントランジスタベースの量子コンピューティングで大規模なパフォーマンスを追求しており、新しい室温デバイスを使用した非常にエネルギー効率の高いコンピューティングのための全く新しいスイッチを追求しています。これらの技術は将来的に物理学における全く新しい概念を使用し、従来のMOSFETトランジスタに取って代わる可能性があります。

Intelは室温で磁電気スピン軌道(MESO)ロジックデバイスの世界初の実験的実証に成功しました。これについてIntelは「スイッチングナノスケール磁石に基づく新しいタイプのトランジスタの潜在的な製造可能性を示しています」と記しました。

さらに、IntelはIMECと共同でスピントロニクス材料の研究を進めており、スピントルクデバイスの実現を目指しています。

加えて、CMOS製造と互換性があり、将来の研究のための次のステップとなるスケーラブルな量子コンピューティングを実現するための完全な300mm量子ビットのプロセスフローも発表しています。

半導体製造に関するさまざまな新情報を発表したIntelは、マレーシアで半導体パッケージング新工場建設のために300億リギット(約8000億円)を投資する計画であることも明らかになっています。

・関連記事

ムーアの法則に黄色信号点滅、Intelの10nmプロセス移行の遅れが確実に - GIGAZINE

「ムーアの法則」の終焉は何を意味するのか? - GIGAZINE

「ムーアの法則」が減速する中で半導体製造企業の取り組みとは? - GIGAZINE

Intelが2兆円超を投じてファウンドリサービスの拡充を目指す「IDM 2.0」を発表、「Apple Siliconの製造を目論んでいる」との指摘も - GIGAZINE

Intelの見直されたプロセスルールと新たなロードマップについてIntel技術幹部が語る - GIGAZINE

・関連コンテンツ