半導体技術がどれだけの進化を遂げているのかが一目でよくわかる「Inside the miracle of modern chip manufacturing」

by Pierre Lecourt

スマートフォンから自動車まで、さまざまなものに搭載されている半導体部品は現代人の生活には欠かせない存在であり、性能向上を目指して半導体の製造技術は日進月歩で進化しています。半導体技術がどのように進化しているのかを視覚化してわかりやすくまとめたコラム「Inside the miracle of modern chip manufacturing」をFinancial Timesが公開しています。

Inside the miracle of modern chip manufacturing

https://ig.ft.com/microchips/

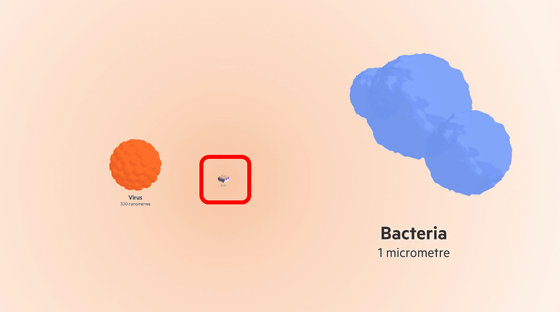

スマートフォンやPC、家電製品に搭載されている半導体部品は、基本的に電気の流れをコントロールする「トランジスタ」で構成されています。最小のトランジスタは約50nmという大きさで、細菌(約1μm)やウイルス(約300nm)よりも小さなサイズです。

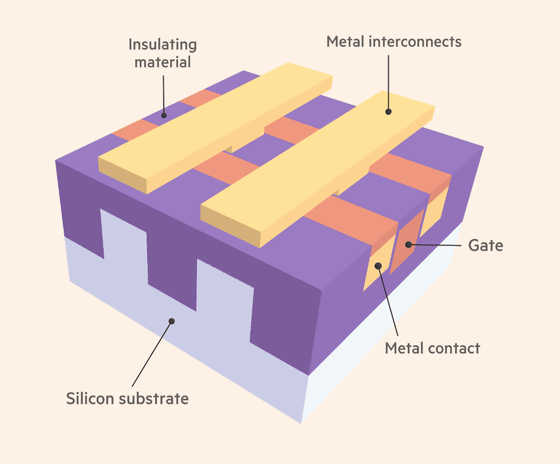

この50ナノメートルというサイズのトランジスタは以下のような構成。シリコン基板(Silicon substrate)に絶縁体(Insulating material)が重なっており、ゲート(Gate)・金属接点(Metal contact)・金属相互接続(Metal interconnects)による回路が搭載されています。

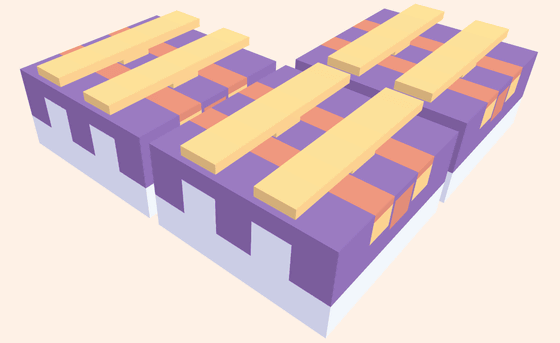

このトランジスタの立体構造と形状で、高密度な集積回路を構成できるというわけです。

Financial Timesは、「50ナノメートルクラスのトランジスタを大量生産できるのは、世界でIntelとSamsung、TSMCの3社だけです」と述べています。たとえば、iPhone 15 Proに搭載されているA17 Proチップは「3nmプロセス」で製造されているといわれています。このプロセスというのは、最小配線のピッチ(間隔)を意味するものでしたが、今はトランジスタの設計の都合もあり、物理的な寸法を示すものではなく、単に技術世代を示すものになりました。

わずか1平方mmに2億個のトランジスタを配置することができ、集積回路全体だとトランジスタの数は数百億規模になります。各メーカーは将来的にトランジスタの密度を上げることで、チップ1枚で1兆以上のトランジスタを搭載することを目指しています。

無数のトランジスタは1枚の集積回路上で相互に接続されています。その配線を1本につないだ長さは、なんと約500kmに至ることもあるそうです。

チップのトランジスタ数を増やすため、各企業は製造技術と設計技術の両方を競争しながら磨いています。半導体ファブであるTSMCやSamsungは製造技術を、NVIDIAやAMDは設計技術を研究し続けています。また、Intelはチップ設計だけではなく、半導体製造事業にも注力することを宣言しており、2027年には1nm相当の10Aプロセスノードを実現する計画を発表しています。

Intelが2027年に「1nmノード」を実現する計画を発表、AIによる自動化工場も - GIGAZINE

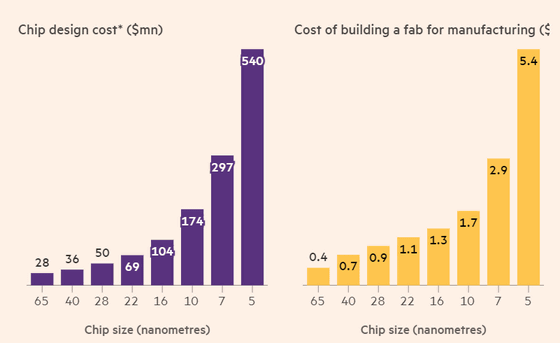

もちろん製造技術・設計技術が進歩するにつれて、チップの設計と製造のコストはどんどん高くなっています。以下の棒グラフはチップの設計コスト(紫)と製造コスト(黄色)を、世代の推移ごとに示したもの。どちらもプロセスルールの世代が進むにつれて、コストが高くなっているのがわかります。

Intelの共同設立者であるゴードン・ムーアは経験則として、「チップ上のトランジスタ数は2年ごとに2倍になる」という「ムーアの法則」を提唱しました。この法則はいつか限界がくるといわれていますが、Intelのパット・ゲルシンガーCEOは2023年に「2年ごとが3年ごとのペースに減速しているものの、ムーアの法則はまだ終わってはいない」と述べています。

ムーアの法則は従来の2年から3年のペースに減速しているがまだ死んでいないとIntelのCEOが語る - GIGAZINE

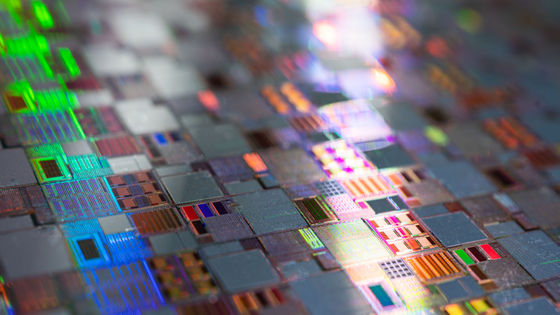

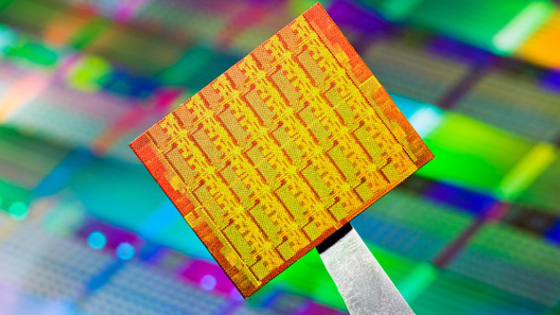

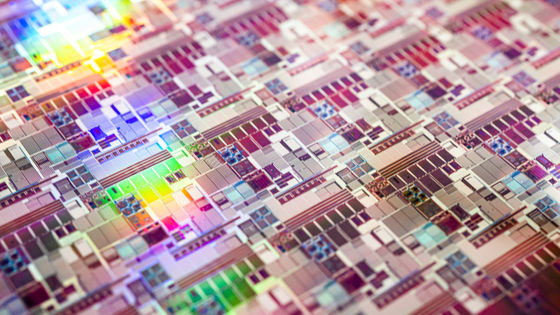

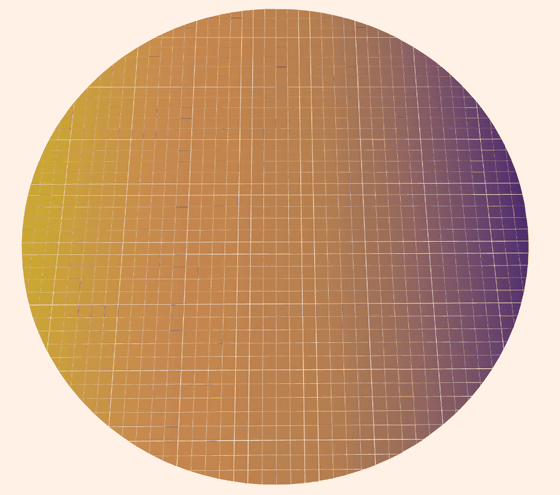

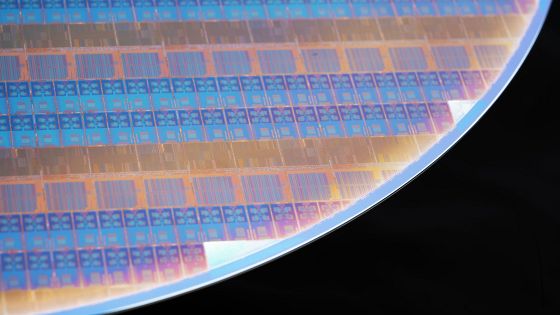

こうした集積回路は、シリコンの塊を薄くスライスしたウエハーから何枚も作られます。

シリコンからどのようにチップを作り出すのかについては、以下の記事を読むとよくわかります。

たった99秒で「CPUの作り方」がわかるムービー - GIGAZINE

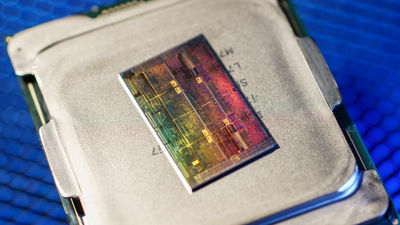

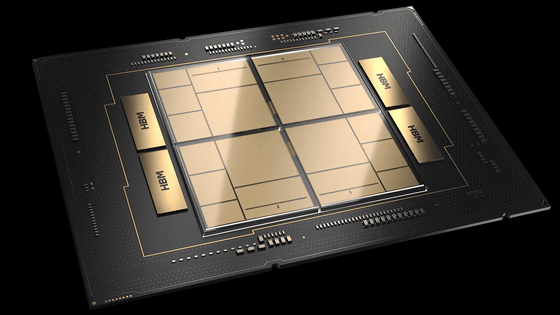

そして、製造したチップを電子機器に適した形に整えるのがパッケージングです。近年はトランジスタを平面に並べるのではなく、立体的に並べて組み立てるのが主流となっています。そして、単一のシリコン上にプロセッサ全体を構築する「システム・オン・チップ(SoC)」から、複数のチップを1つのダイに載せて構成する「マルチ・チップ・モジュール(MCM)」に移行しています。

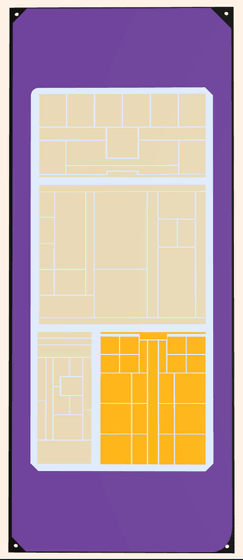

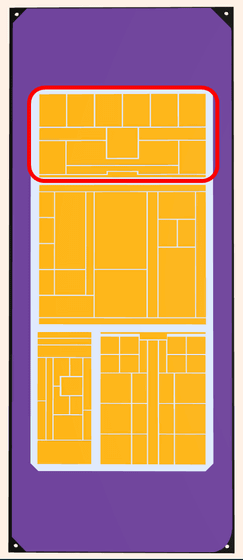

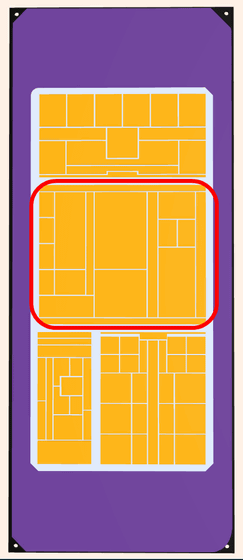

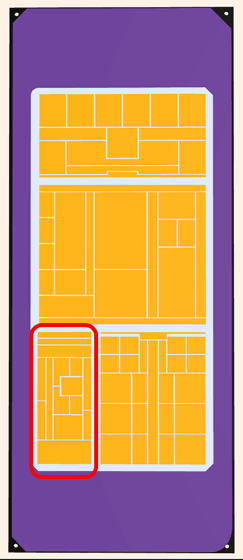

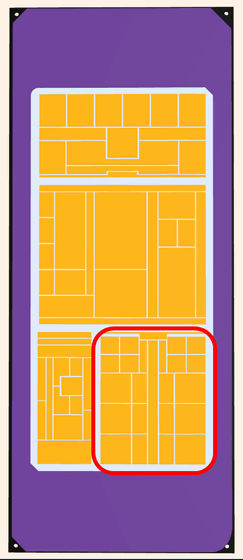

たとえば、IntelのMeteor Lake世代のマイクロプロセッサは、シリコン基板上にチップレットのタイルを配置することで構成されています。パッケージ全体の大きさは50mm×25mmです。

一番上はグラフィック関係の処理をする「グラフィックタイル」

その下にあるのはメモリの制御やAIの処理を担当する「システムタイル」

「I/Oタイル」は接続関連を担当し、コンポーネント同士や接続した外部と効率的に通信できるようにします。

「コンピューティングタイル」はいわゆるCPUに当たる部分で、パフォーマンスと効率を監視します。

このMCMによるパッケージ構成がムーアの法則を存続させる方法だといわれており、各社も同様の方向で設計をしています。また、MCMは柔軟性にも富んでおり、要件に応じてチップレットを交換すればいいので、さまざまな顧客に対応できるのもメリットです。

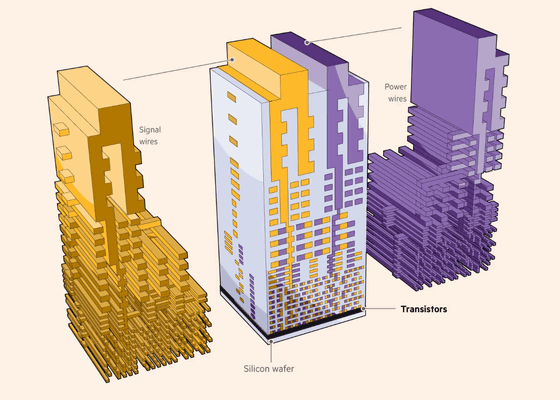

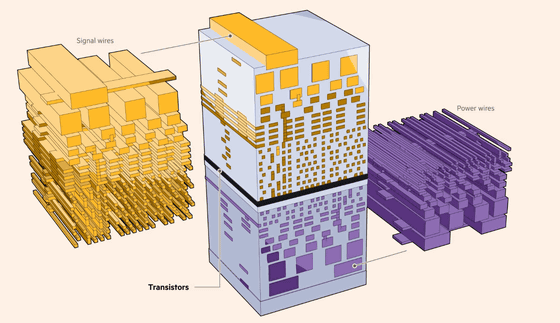

さらにトランジスタそのものの構造も近年見直されています。従来のチップアーキテクチャでは信号線(Signal wires)と電力線(Power wires)がシリコン基板の表面にありました。そのため、電力線と信号線が場所を取り合うようになり、発熱や信号遅延の原因となり、性能低下の原因となります。

そこで各半導体メーカーは電力線をシリコン基板の裏面に移動させる「裏面電力供給技術」を開発しています。

たとえば、Intelは2023年に発表した「Intel PowerVia」は裏面電力供給技術の一種で、「この技術によって2030年までにパッケージに1兆個のトランジスタを詰め込める」とIntelはアピールしました。

Intelが「ムーアの法則」を再出発させる裏面電力供給技術「PowerVia」のテストに成功、Intelは「ライバルの2年先を行く」「ピザ作りをやめる」とアピール - GIGAZINE

さらに、現行の集積回路は電子を利用していますが、発光素子や受光器などを使ってより高速かつ省電力の集積回路を作る「シリコンフォトニクス」の開発についても各半導体メーカーがしのぎを削っています。

Intelの先進トランジスタ開発部門のディレクターであるクリス・オース氏は「半導体は私たちの日常生活において不可欠なものであり、あって当然のものだと思っています。チップ開発を可能にする科学の飛躍を考えると、今後20年間で何ができるのかが楽しみです」と述べています。

また、TSMCのパスファインディング担当ヴァイスプレジデントのミン・カオ氏は「TSMCのエンジニアは新世代のチップを定期的なペースで開発できます。顧客がそれを求めているからです。誰も求めなくなったら止まりますが、そうはなりません」と語りました。

・関連記事

台湾の半導体メーカー「TSMC」の熊本工場がついに完成、さらに第2工場の建設に約7300億円の補助金の交付を日本政府が決定 - GIGAZINE

IntelがAI時代に適応した拡張プロセスロードマップやエコシステムパートナーの拡大を発表、2030年までに世界2位のファウンドリを目指す - GIGAZINE

Apple A4チップやAMD Ryzenの生みの親であるジム・ケラー氏がNVIDIAのCUDAとx86アーキテクチャを「沼」と呼んで批判 - GIGAZINE

ソフトバンク創設者の孫正義氏が15兆円の資金を投入してNVIDIAに対抗するAI半導体ベンチャーを設立する「プロジェクト・イザナギ」を推進か - GIGAZINE

OpenAIのサム・アルトマンCEOが数百兆円という桁外れの資金調達を計画し「半導体業界の再構築」を目指している、すでに孫正義やUAEの有力者と会談しているとの報道も - GIGAZINE

中国の半導体メーカー・SMICがアメリカの規制を乗り越えてファーウェイのHiSiliconが設計した5nmプロセスのチップを製造することが明らかに - GIGAZINE

台湾のチップメーカー「TSMC」が日本に第2工場を建設し2027年末までに操業を開始すると発表、総投資額は約3兆円となり第1工場は第4四半期に量産開始予定 - GIGAZINE

・関連コンテンツ

in ハードウェア, Posted by log1i_yk

You can read the machine translated English article ``Inside the miracle of modern chip manu….