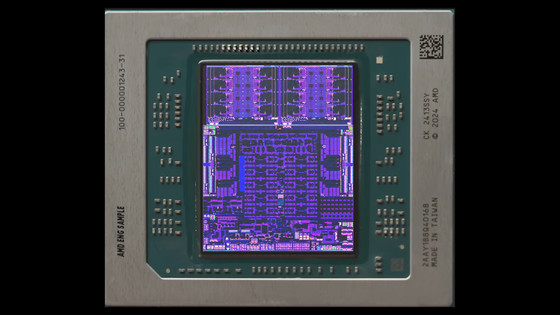

Intel・AMD・Microsoft・TSMC・Samsungなどがチップレットの新規格を策定する「UCIe」コンソーシアム設立を発表

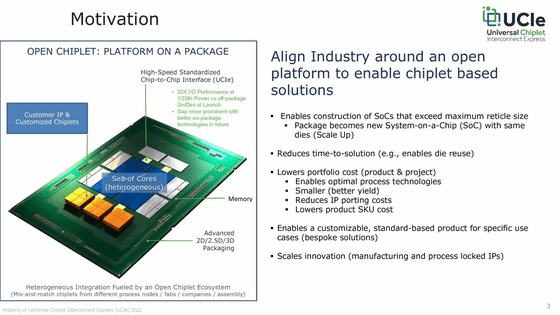

IntelやAMD、Arm、Qualcomm、TSMC、Samsungなどの半導体企業や、MicrosoftやMetaなどのテック企業が集まり、別プロセスで生産したコンポーネントを組み合わせて1つのSoCを構築する「チップレット」の新規格を策定するための団体「Universal Chiplet Interconnect Express(UCIe)」を立ち上げました。同時に、複数のシリコンダイを1つのパッケージに統合するためのオープンで相互運用可能な新規格「UCIe 1.0」の仕様も明らかとなりました。

Home | My Site

https://www.uciexpress.org/

Universal Chiplet Interconnect Express (UCIe) Announced: Setting Standards For The Chiplet Ecosystem

https://www.anandtech.com/show/17288/universal-chiplet-interconnect-express-ucie-announced-setting-standards-for-the-chiplet-ecosystem

Intel, AMD, and other industry heavyweights create a new standard for chiplets | Ars Technica

https://arstechnica.com/gadgets/2022/03/intel-amd-and-other-industry-heavyweights-create-a-new-standard-for-chiplets/

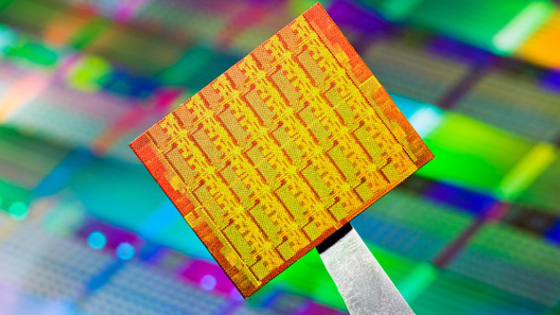

これまではCPUやGPU、SRAMなどの機能をすべて1枚のシリコンダイに詰め込んだSoC(System on Chip)が作られていました。しかし、1枚にすべての機能を盛り込むと、すべての機能を1つのプロセスノードで生産することになります。そこで、各機能をそれぞれ適したプロセスノードで生産し、それぞれをまるでレゴブロックのように組み合わせてチップを設計するという概念として、「チップレット」が登場しました。

チップレットはダイごとに最適なプロセスノードで生産することで、チップの歩留まり率が向上してコストパフォーマンスを改善できるというのが大きなメリット。チップレットの提唱は、「半導体回路の集積密度は1年半から2年で2倍となる」というムーアの法則に限界がきたといわれる中で、プロセッサに要求される性能が非常に高くなり、必然的にチップ生産のコストパフォーマンスのさらなる向上を求められたことが背景にあります。

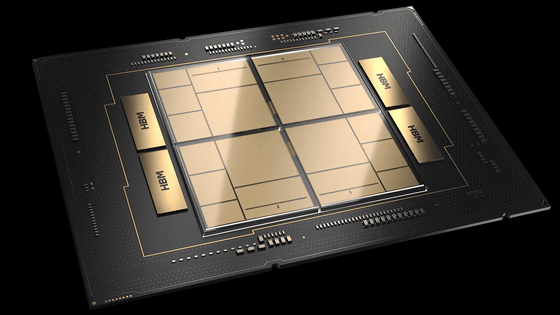

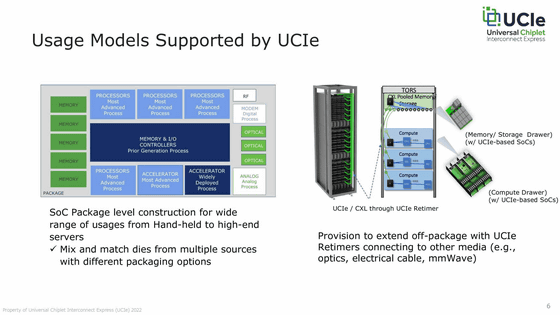

AMDのRyzenシリーズやIntelのSapphire Rapids世代Xeonなど、すでにチップレットを設計に採用したプロセッサは登場していますが、これらのチップレットで使われているダイの相互接続規格は異なります。今回提唱されたUCIe規格は、このダイを相互接続する方法を単一の規格に定めることで、「将来的にある企業が同業他社のシリコンダイを自社製品に組み込む」「中小企業が独自のチップレット設計を行う」といったことも可能になります。

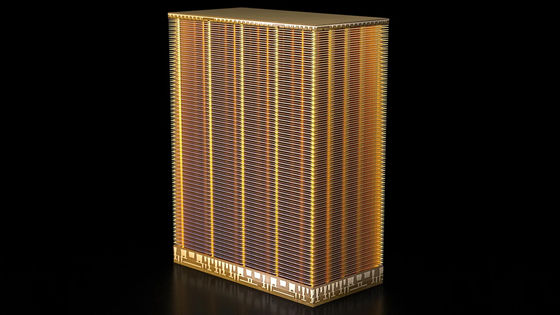

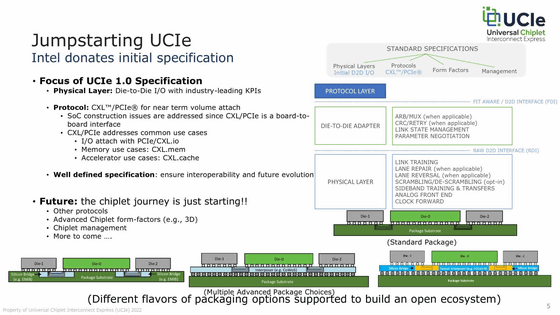

今回発表されたUCIe 1.0は、Intelが開発して2020年にオープンな技術となったAdvanced Interface Busテクノロジーをベースに策定されているとのこと。チップレットのダイが相互通信するための電気信号の規格や物理レーン数、バンプのピッチが規格化され、さらに相互通信のプロトコルが定義されています。ただし、UCIe 1.0はチップレットのダイをどのように相互接続するかについて定めている一方で、ダイとダイの接続をどのように設計するかというパッケージング技術やブリッジング技術はUCIeに含まれていません。

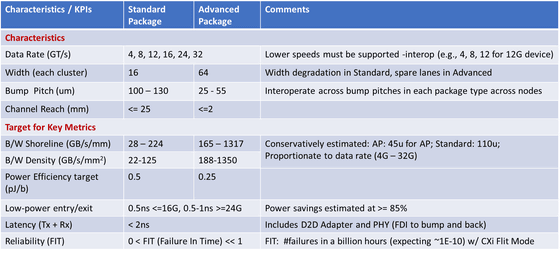

また、UCIe 1.0では「スタンダードパッケージ」「アドバンスドパッケージ」という2つの異なるパフォーマンスレベルが用意されています。従来の有機基板を想定しているというスタンダードパッケージは最大16データレーンでチップ間のスペースは25mmですが、アドバンスドパッケージは最大64データレーンでチップ間のスペースはわずか2mmになります。

UCIeの基盤となるチップレット間通信プロトコルは、PCIeと関連のあるCompute Express Link(CXL)になっています。しかし、AMDのInfinity Fabricのように独自開発のプロトコルでも、UCIeの仕様に準拠したまま使用できるとのこと。

UCIeに参加する企業は以下の通りで、Intel・AMD・Arm・Qualcommといったファブレス企業やTSMC・Samsung・ASE Groupといったセミコンダクターに加えて、MicrosoftやGoogle、Metaも名を連ねています。

UCIeの策定と普及が進めば、「IntelのCPUにAMDのGPUを組み合わせる」ということも可能になるかもしれません。UCIe 1.0の細かい仕様については以下のページでダウンロード可能のホワイトペーパーを見ることが可能です。

Specification | My Site

https://www.uciexpress.org/specification

・関連記事

たった99秒で「CPUの作り方」がわかるムービー - GIGAZINE

ハードウェアの発展を阻害しているのは「マザーボード」だという指摘、マザーボードに代わる次世代技術とは? - GIGAZINE

Intelが次期CPUアーキテクチャ「Sunny Cove」、内蔵GPU「Gen11」、ディスクリートGPU「Xe」などを発表 - GIGAZINE

Intel・NVIDIA・TSMCは半導体業界でどんな役割を果たしているのか? - GIGAZINE

半導体不足解消と復権を狙うIntelの次の一手とは? - GIGAZINE

・関連コンテンツ

in ハードウェア, Posted by log1i_yk

You can read the machine translated English article Intel, AMD, Microsoft, TSMC, Samsung, et….