Intel, AMD, Microsoft, TSMC, Samsung, etc. announce the establishment of the 'UCIe' consortium to formulate new chiplet standards

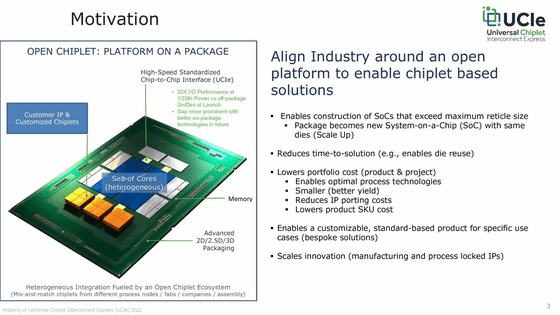

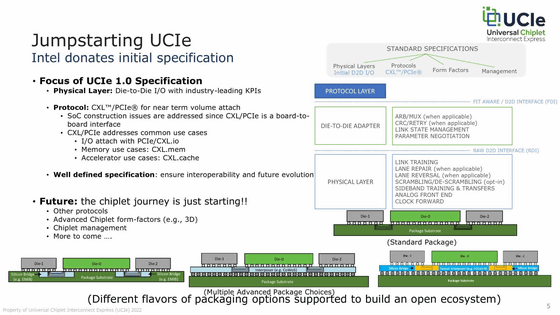

Semiconductor companies such as Intel, AMD, Arm, Qualcomm, TSMC, Samsung, and tech companies such as Microsoft and Meta gather to create a new standard for 'chiplets' that build a single SoC by combining components produced in different processes. We have launched the ' Universal Chiplet Interconnect Express (UCIe) ', an organization for formulating. At the same time, the specifications of a new open and interoperable standard ' UCIE 1.0 ' for integrating multiple silicon dies into one package have been revealed.

Home | My Site

Universal Chiplet Interconnect Express (UCIe) Announced: Setting Standards For The Chiplet Ecosystem

https://www.anandtech.com/show/17288/universal-chiplet-interconnect-express-ucie-announced-setting-standards-for-the-chiplet-ecosystem

Intel, AMD, and other industry heavyweights create a new standard for chiplets | Ars Technica

https://arstechnica.com/gadgets/2022/03/intel-amd-and-other-industry-heavyweights-create-a-new-standard-for-chiplets/

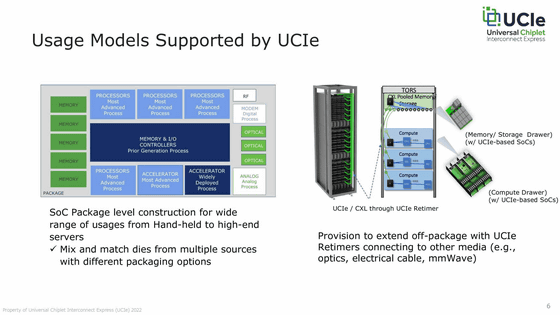

Until now, SoCs (System on Chip) have been created in which all functions such as CPU, GPU, and SRAM are packed in one silicon die. However, if you include all the functions in one sheet, you will produce all the functions in one process node. Therefore, 'Chiplet' was introduced as a concept of producing each function with a suitable process node and designing a chip by combining each function like a Lego block.

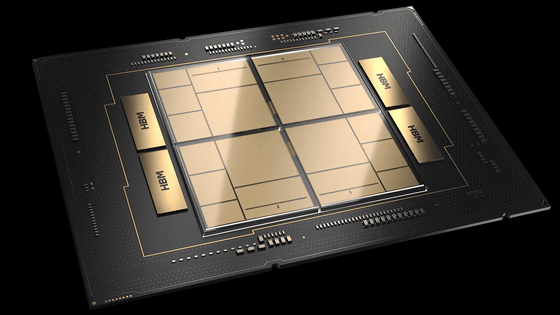

By producing chiplets at the optimum process node for each die, the major merit is that the yield rate of chips can be improved and cost performance can be improved. Chiplet's proposal is that the performance required for processors has become extremely high, while Moore's law that 'the integration density of semiconductor circuits doubles in one and a half to two years' is said to have reached its limit . Inevitably, the background was that we were required to further improve the cost performance of chip production.

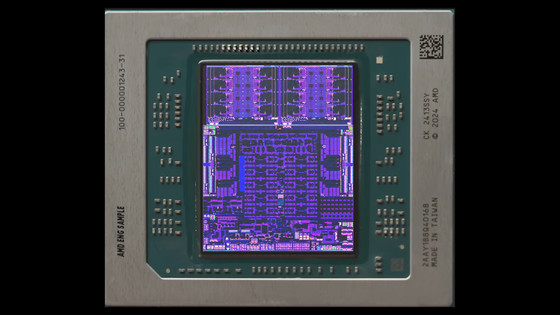

Processors that have already adopted chiplets in their designs, such as AMD's Ryzen series and Intel's Sapphire Rapids generation Xeon, have already appeared, but the die interconnection standards used in these chiplets are different. The UCIe standard proposed this time defines a single standard for how to interconnect the dies, so that 'a company in the future will incorporate silicon dies of other companies in the same industry into their products' and 'small and medium-sized companies will have their own chips.' It is also possible to do a let design.

UCIe 1.0 announced this time is said to be formulated based on

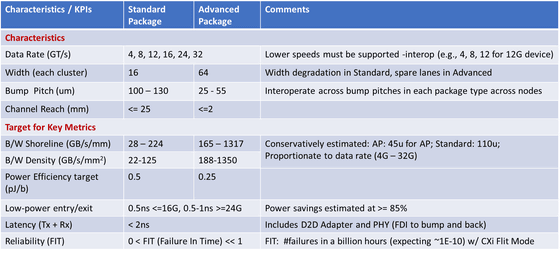

In addition, UCIe 1.0 offers two different performance levels: 'Standard Package' and 'Advanced Package'. The standard package, which assumes a conventional organic board, has a maximum of 16 data lanes and a space between chips of 25 mm, while the advanced package has a maximum of 64 data lanes and a space between chips of only 2 mm.

The underlying inter-chiplet communication protocol for UCIe is the

The companies participating in UCIe are as follows, including fabless companies such as Intel, AMD, Arm and Qualcomm, semiconductors such as TSMC, Samsung and ASE Group, as well as Microsoft, Google and Meta.

As UCIe develops and becomes more widespread, it may be possible to 'combine an AMD GPU with an Intel CPU.' You can see the downloadable white paper on the following page for the detailed specifications of UCIe 1.0.

Specification | My Site

https://www.uciexpress.org/specification

Related Posts:

in Hardware, Posted by log1i_yk