「36コアチップ」の試作品をMITの研究者が開発

by Windell Oskay

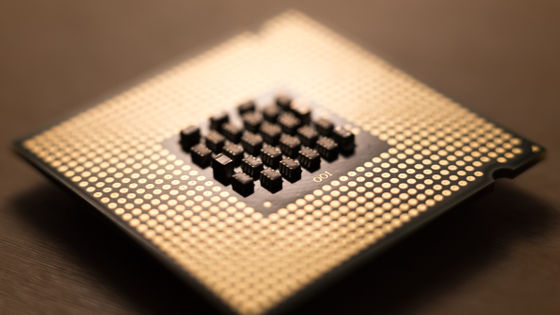

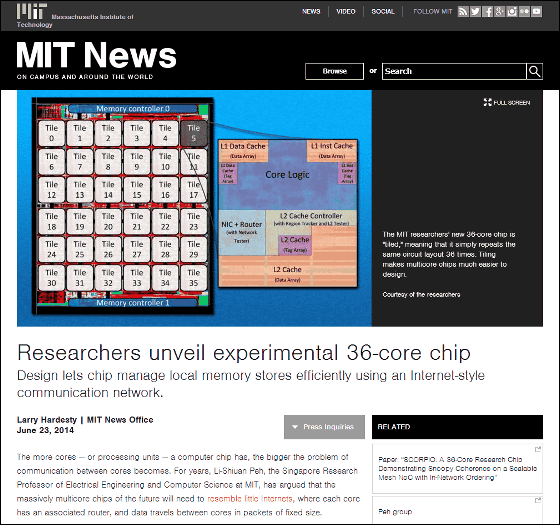

1つのプロセッサの中に複数のコアを持つマルチコアはPCやスマートフォン向けのチップにおいて珍しいものではない技術ですが、搭載するコアを36個に増やしたチップをMITの研究者が開発しました。

Researchers unveil experimental 36-core chip | MIT News Office

http://newsoffice.mit.edu/2014/researchers-unveil-experimental-36-core-chip-0623

Li-Shiuan Peh教授は以前から、マルチコアのチップに搭載されるコアの数が増えれば増えるほどコア間の通信での問題が大きくなることを指摘。将来的にコア間にルーターのようなものを置いてデータのやりとりを整理し、いわば「小さなインターネット」のような形にする必要があると主張していました。

現在、マルチコアの主流はデュアルコア(コア2つ)・クアッドコア(コア4つ)・オクタコア(コア8つ)で、コア同士はバスと呼ばれる経路で結ばれています。このコア間同士で通信が行われるとき、1つのコアがバスに対する排他的アクセス権を持つことになるので、その間、他のコアは通信することができないため、本来転送にかかる時間よりも多くの時間が必要となります。

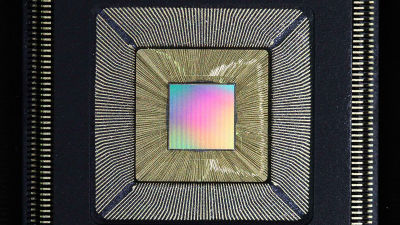

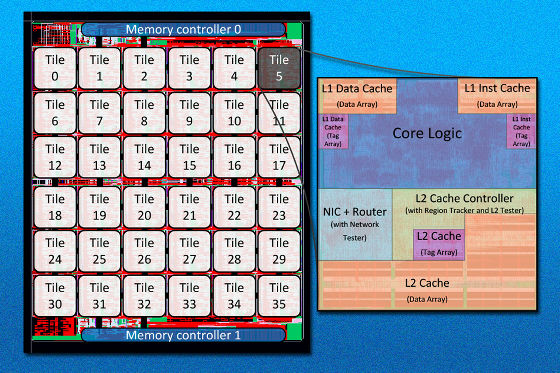

今回、Peh教授らのグループが発表したのは36コアのチップで、隣接したコアと直接接続する「ネットワーク・オン・チップ(NoC)」の特徴を持ちます。これにより、使用中のコアを避けた通信経路を確立することができるので、効率的に動作することができるというわけです。

Courtesy of the researchers

しかし、NoCのコンセプトの問題として、データが追跡不可能な経路を通って目標のコアへ到達するという点があります。これは、プロセッサ上のコアがときどき、メインメモリに返される前に、他のコアのキャッシュに格納されたデータへアクセスしようとするため。この問題点は、これまでのバス接続のコアと同じ方法でデータパケットを探すシャドウネットワークをチップに装備することで解決しています。

研究チームは、今回開発した36コアチップを搭載することで実際にアプリケーションがどのように動作するのか、Linuxに修正を加えて確かめる予定だとのこと。また、このチップは今後、誰でも入手・利用可能なオープンソースハードウェアとして公開されることになっています。

・関連記事

スマートフォンから体内の小型チップ経由で血液データをチェックできる技術が登場 - GIGAZINE

世界最小128ギガビットNANDフラッシュメモリーチップが登場 - GIGAZINE

GPSなしでのナビを実現する超小型チップをDARPAが開発 - GIGAZINE

マイクロチップの簡単な「開き方」と中身がどうなっているのか - GIGAZINE

4Kムービー撮影対応・GPU2倍・より省電力のスマホ用2.3GHzクアッドコアCPU「Snapdragon 800」 - GIGAZINE

・関連コンテンツ

in ハードウェア, Posted by logc_nt

You can read the machine translated English article MIT researchers developed prototypes of ….