既存の2D半導体から大幅な性能向上が期待できる「3Dチップ」の製造に成功

これまでのように平面上へパーツを敷き詰めた半導体ではなく、パーツの層を縦に積み上げた「3Dチップ」が開発されました。これにより、従来の「2Dチップ」と比較してスループットが4倍向上するなど大幅な改善が見られたとのことです。

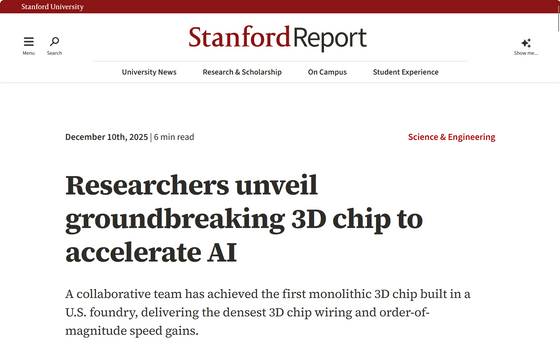

Researchers unveil groundbreaking 3D chip to accelerate AI | Stanford Report

https://news.stanford.edu/stories/2025/12/monolithic-3d-chip-foundry-breakthrough-ai

First truly 3D chip fabbed at US foundry, features carbon nanotube transistors and RAM on a single die — future devices could have up to 1000x improvement in energy-delay product | Tom's Hardware

https://www.tomshardware.com/tech-industry/semiconductors/stanford-led-team-builds-3d-ai-chip-at-us-foundry-reports-4x-performance-gains

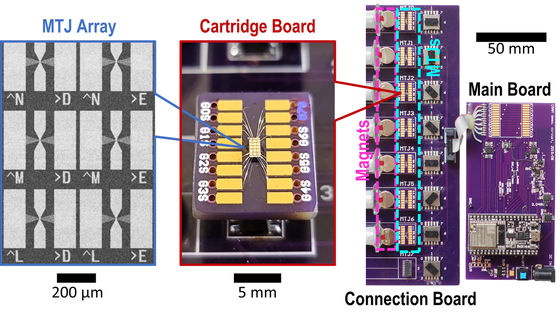

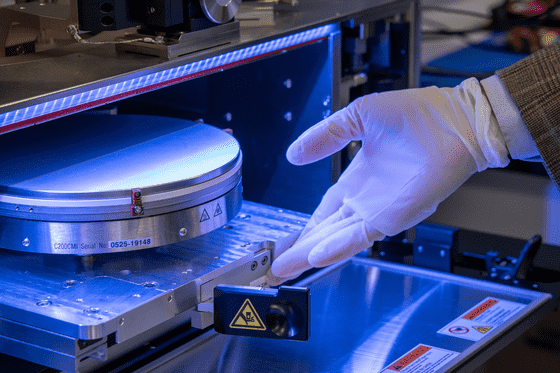

スタンフォード大学、カーネギーメロン大学、ペンシルベニア大学、マサチューセッツ工科大学のエンジニアが、半導体ファウンドリ企業であるスカイウォーター・テクノロジーと共同で行った研究開発により、商用のファウンドリで初めて3Dチップが開発されました。

ChatGPTやClaudeのような現代のAIモデルは、情報を保存する「メモリ」と処理を行う「演算ユニット」の間で膨大な量のデータを往復させなければなりません。

従来の2Dチップでは、部品が単一の平面上に配置され、メモリが限られた範囲に分散しているため、データは数本の長く混雑した経路を移動せざるを得ませんでした。チップ上に十分なメモリを近接配置できない制約からシステムは常に情報待ちの状態に陥るため、ボトルネックが生じ、エンジニアはこのボトルネックを「メモリの壁」と呼んで既存のチップ設計には限界があると見なしていました。

数十年にわたり、チップメーカーはメモリの壁問題に対処するため、計算とデータ保存を担う微小なスイッチ「トランジスタ」を縮小し、各チップに多くのトランジスタを詰め込む手法を取ってきました。しかしこの戦略も、研究者が「微細化の壁」と呼ぶ物理的な限界に近づきつつありました。

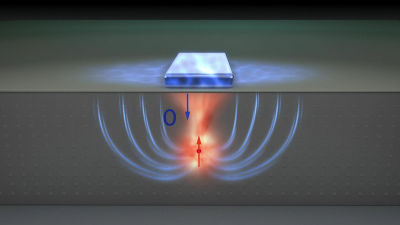

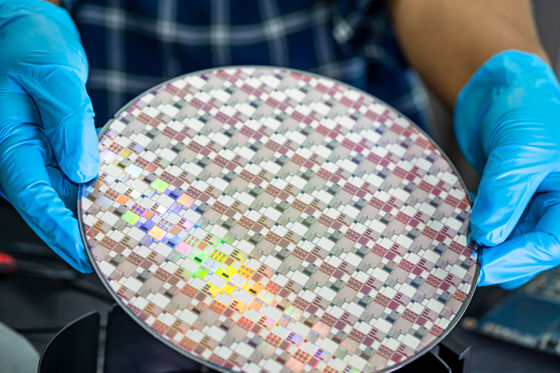

新しい3Dチップは、メモリと演算処理を垂直方向に統合することで性能を向上させる半導体です。「3Dチップ」というものは過去にも存在しましたが、そのほとんどは個別のチップを積層する手法に依存していたため、層の間の接続は粗く、ボトルネックが生じやすいという課題がありました。スタンフォード大学の研究者らは、別々のチップを製造してから融合させる代わりに、各層を連続したプロセスで積み上げる「モノリシック」手法で階層を構築。これにより、部品をはるかに高密度に接続することに成功しました。

論文の筆頭著者であるカーネギーメロン大学電気・コンピュータ工学科助教授タタガタ・スリマニ氏は「3Dチップは、高層ビルのエレベーター群が多くの居住者を同時に移動させるように、はるかに多くの情報を高速で移動できます」と説明しました。

初期のハードウェアテストでは、3Dチップのプロトタイプが同等の2Dチップを約4倍上回る性能を示しており、メモリと演算ユニットの積層層数を増やした高層版をシミュレーションした結果、さらなる性能向上が見込まれたとのこと。高層版では、MetaのAI「LLaMA」モデル等を利用した実際のユースケースにおいて、最大12倍の改善が確認されました。

実験的な3Dチップの開発例は過去にも存在しますが、明確な性能向上を示し、商業ファウンドリで製造されたのは今回が初めてとのこと。

最も注目すべきは、この設計が速度とエネルギー効率のバランスを取る重要指標であるエネルギー遅延積(EDP)において、100倍から1000倍の改善を実現する道を開く点だと研究者らは述べています。データ移動を大幅に短縮し、より多くの経路を追加することで、チップは従来型の平面アーキテクチャでは達成不可能と見なされてきた「高いスループット」と「演算単位あたりの低消費電力」の両立を実現するとされています。

論文共著者でスカイウォーター・テクノロジーの技術開発オペレーション担当副社長であるマーク・ネルソン氏は「今回の研究は、こうした先進的なアーキテクチャが研究室だけでなく、国内で大規模に生産可能であることを示しています。半導体イノベーションの最前線に立つためにアメリカが必要としているのはまさにこれなのです」と述べました。

・関連記事

半導体の放熱素材としてダイヤモンドコーティングすることでピーク温度の抑制に成功 - GIGAZINE

原子数個レベルの超極薄でありながら動作する32ビットRISC-Vプロセッサを開発することに科学者らが成功 - GIGAZINE

Intelが18A(1.8nm)プロセスの半導体の初期生産を開始 - GIGAZINE

・関連コンテンツ

in ハードウェア, Posted by log1p_kr

You can read the machine translated English article Successfully manufactured '3D chip' that….