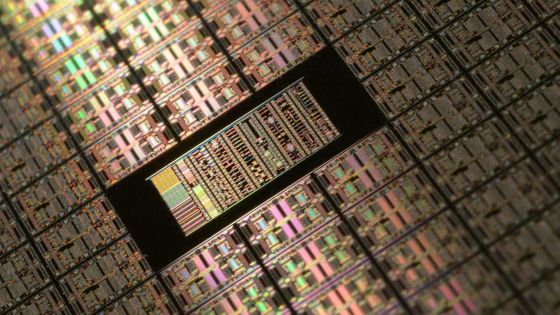

下図は2000年代初頭のCMOSチップの構造を図に表したもの。チップの下部にある「FEOL」とマークされた領域にトランジスタなど半導体の主要パーツが設置されており、上のBEOL層で多数のパーツが相互に接続されています。使用されるトランジスタ数の増加とともに配線は複雑になっており、10層以上も配線用のBEOL層があることは珍しくありません。

By Cepheiden

チップはこの複雑な構造を1層ずつ積み上げて作成されます。

By Fabrication Engineering at the Micro- and Nanoscale

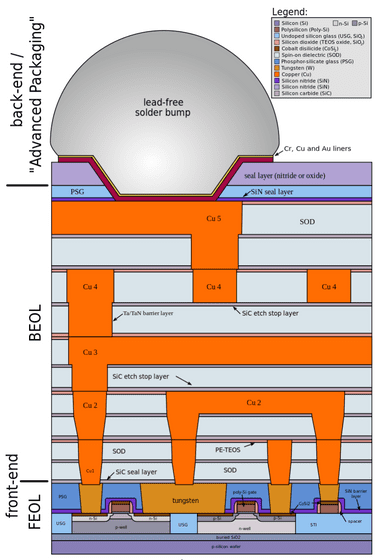

チップの構造を構築する際には「レイヤリング」「パターニング」「ドーピング」「熱処理」という4つの操作を行います。

・レイヤリング

わずか1ナノメートルという髪の毛の10万分の1の薄さの層をウェハの表面に追加します。技術の進歩と共に積層にも高い精度が要求され、現代の原子層堆積法では単一の原子層を作成できるようになっています。

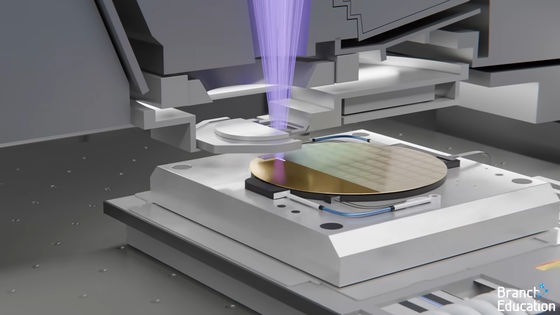

・パターニング

ウェハの上に特定のパターンを刻み、必要に応じて材料を選択的に除去します。現代ではフォトリソグラフィーが使用されており、感光性の材料をコーティングしてからパターンが刻まれているマスクプレートを通して光を当て、化学反応を発生させてパターンを「印刷」しています。

・ドーピング

半導体の材料に非常に少量の不純物を導入し、導電率を変化させます。不純物の違いによって自由電子が過剰なn型半導体と正孔が過剰なp型半導体が生成され、n型半導体とp型半導体を適切に配置することでトランジスタを作成できます。

![]()

By MKS

かつてはガス化した原子をウェハに反応させることでドーピングを行っていましたが、現代ではイオンビームを照射してドーピングを行います。

![]()

By Xiao 2012

・熱処理

イオンビームを照射するとシリコンの結晶構造が損傷するため、数秒で1000度までウェハを加熱した後ゆっくり冷却するという熱処理を行って結晶構造を修復します。

![]()

By Xiao 2012

半導体の製造工程には4つの基本となるプロセス以外にも多数のサブプロセスが存在しています。サブプロセスの1つが「研磨」です。半導体は数多くの層で構築されるため、層が追加されるごとに厚さのばらつきが大きくなってしまいます。表面を滑らかにするため、化学機械研磨(CMP)を使用してウェハを研磨しています。

![]()

By Chris Mack

また、CMPはエッチングによって生じた穴を埋めるためにも使用されます。

![]()

By Envido32

「洗浄」はもう一つの重要なサポートプロセスです。非常に小さな浮遊粒子であっても半導体の誤動作を引き起こすため、ウェハは溶剤と純水で常に洗浄する必要があります。また、工程の多くの部分は浮遊粒子を極限まで減らしたクリーンルーム内で行われ、プロセスのさまざまなポイントでウェハを測定してミスや欠陥がないかを判断しています。

![]()

By Xiao 2012

4つのメインプロセスと多数のサブプロセスを繰り返し適用することで半導体の構造がゆっくりと構築されていきます。現代の製造工程では80枚以上のマスクと数千回のプロセスステップが必要です。

![]()

By Embedded Associated

回路の構造が完成すると、組み立て・パッケージングへと進みます。組み立て・パッケージングプロセスではウェハが個別のチップへと分割され、それぞれのチップがワイヤに接続されてから保護コーティングを施されます。

半導体はプロセスステップが多い複雑な製品というだけでなく、サイズが非常に小さいため極端な精度が要求されます。一般的な製造工程では0.05mm~0.2mm程度の誤差まで許容できるのに対し、半導体の場合はそもそもプロセスゲート間の距離が0.000051mm(51nm)しかありません。また、1つの粒子が紛れ込んで回路をショートさせるとチップ全体が機能しなくなってしまいます。

![]()

半導体製造の歴史は破壊的な影響を与える小さな要素との戦いの記録です。1940年代にベル研究所で半導体が研究されていた際に謎の部品故障が発生しましたが、その原因は研究者が銅製のドアノブに触れたことで手に付着したわずかな銅原子でした。また、初期の半導体メーカーは半導体の歩留まりが月の満ち欠けや従業員のトイレのタイミング、女性従業員の月経周期などに影響されることに気付いていました。

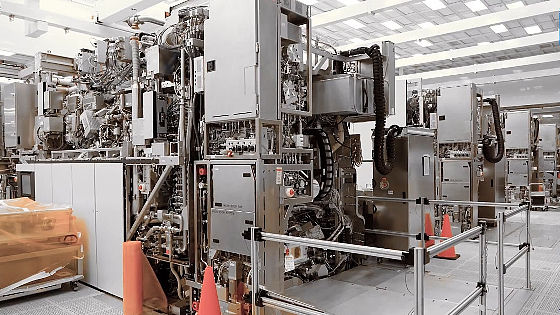

半導体技術の進化と共に、製造時に要求される清浄度合いも向上していきました。現代の半導体工場ではクリーンな環境を作り出すために4つの階層を備えています。一番上にはファンやフィルターが設置されており、2階層目にあるクリーンルームの空気循環を支えています。クリーンルームの下には2層のサポート用の層があり、クリーンルームの設備用の配管・配線・機器が設置されています。

![]()

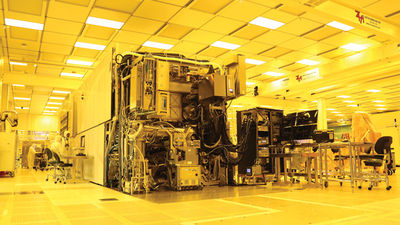

By Intel

クリーンルームにはリソグラフィー装置のほか、化学蒸着装置やイオン注入装置、洗浄およびエッチング用のウェットベンチなどさまざまな半導体製造用装置が設置されます。ツールは種類ごとにまとめて設置されており、それぞれの工程で使用される化学物質を隔離しています。また、柱や壁の影響を最小限に抑えるため、屋根を大きくて長いトラス構造にすることでクリーンルームのスペースを可能な限りオープンにしてあります。

![]()

By TaiwanPlusDocs

Intelの半導体工場の建設中の様子を見ると、クリーンルーム用の巨大なトラス構造が確認できます。

![]()

By Intel

一般的な住宅には空気1立方フィートあたり0.5μm以上の粒子が50万個程度存在しており、外科手術室でも10万個程度の粒子が浮遊していますが、半導体工場のクリーンルームではクラスによって空気1立方フィートあたり0.5μm以上の粒子が10個~100個以下になるよう管理されています。粒子の侵入を防ぐため、クリーンルームは外部に対して正圧に保たれており、1時間あたり5~10回空気が入れ替わる頻度で換気されています。

![]()

By MKS

ウェハに直接触れる空気は1立方フィート内に0.5μm以上の粒子が0.1個以下というさらに高い清浄度が必要になるため、メーカーはクリーンルーム内にさらにミニクリーンルームを作成し、ウェハをその中で処理しています。装置と装置の間の輸送にはFOUPという密閉されたポッドが使用されています。

![]()

現代の工場ではFOUPは天井に取り付けられたレールシステムで構成されています。製造プロセス数が多いためウェハが工場を通過するのにかかる期間は数カ月にわたり、常に数万枚のウェハが工場内に存在することになります。こうした大量のウェハを処理するため、輸送システムは何kmもの線路と数千の輸送車両を備えた上でスムーズにトラフィックを処理できるものである必要があります。

![]()

By Intel

製造プロセスに影響を与えるのは浮遊粒子だけではありません。半導体工場は振動にも非常に敏感で、過去には工場から100m離れた排気口がクリーンルームの床に許容できない振動を与えていたケースが存在していました。工場は従来の建物の100倍の機械エネルギーと50倍の空気の流れを吸収し、振動を人間の知覚のしきい値よりも数桁低く抑える必要があります。下図はさまざまな建物の振動要件ですが、半導体工場はVC-DもしくはVC-Eに従って建築されています。

![]()

By Bayat et al 2012

振動を最小限に抑えるため、クリーンルームの床は1m程度の深いコンクリートワッフルスラブ構造で構築され、できるだけ堅くするために密に配置された柱で支えられています。スラブの上には金属製の床が設置され、製造機械を人間の通る床から切り離しています。リソグラフィー装置など特に厳格な要件が必要となる機器には振動を感知して打ち消すアクティブ振動ダンパーなどの対策が必要です。

![]()

By TMC

場合によってはクリーンルームの床を建物の他の部分の床と物理的に切り離した構造が採用される場合もあります。

![]()

By Bayat et al 2012

クリーンルームの建設だけでなく、製造装置に接続するパイプや薬品の保管などを含めると半導体工場の建設には広大な敷地と大量の資材、そして特別な工法が必要となり費用が高額になることは不思議なことではありません。しかし、現代の半導体工場では工場の建設費よりも中で使用する製造装置の費用が高額になっています。1980年代には建設費と製造装置の費用が半々程度でしたが、1990年代後半には既に製造装置の費用がコストの大部分を占めるようになっていました。

![]()

By Art et al 1994

製造装置のなかでもリソグラフィー装置の費用は特に高額で、リソグラフィー装置だけで工場の建設費と同等の費用がかかる場合もあります。リソグラフィー装置に続き、蒸着・洗浄・エッチング用の装置のコストが高くなっています。

![]()

By IFP

半導体製造技術が向上し、トランジスタが小さくなるにつれて半導体製造工場の費用も上昇しています。プロセスノードが高度化すると製造装置の費用が高額になるほか、より多くの層が必要で工程のステップ数も増加するため、1段階高度化するたびに製造コストは30%増加します。

![]()

By Practices of Wafer Fab Operations

また、工場コストの上昇は半導体産業の構造を引き起こしました。工場が安価だったころはどのチップメーカーも独自の工場を建設する余裕がありましたが、製造コストが上昇するにつれてそのコストをまかなえる生産量を持つメーカーは少なくなりました。例えば150mmウェハ製造工場を効率的に運用する場合は毎月1万ウェハを処理できればOKですが、300mmロジックウェハを製造する工場の場合、最高効率を出すためには毎月4万ウェハを処理する必要があります。

したがって、最先端の半導体を製造するのはTSMCやSamsung、Intelなど少数の企業だけになり、AppleやNVIDIAなどの企業はチップを設計して半導体製造工場を所有するTSMCなどの「ファウンドリ」に製造させるようになりました。ファウンドリ側はさまざまなチップ企業の注文を受け付けることで最先端の工場を効率的に運用するための規模を達成できるというわけです。

こうして半導体工場の規模は巨大化し、さらに巨大な工場の中で24時間365日にわたって原子レベルの操作をし続ける必要があるという要因によって工場の建設費用は巨額になってしまいました。