なぜ米国防総省のDARPAは古いプロセスルールで最新型チップを作ろうと莫大な費用を投じるのか?

SamsungやTSMCが7nmプロセスを採用した最新チップの量産態勢に入っています。これまで半導体チップの性能向上に大きく寄与してきた微細化技術に限界が見え始めている中で、アメリカ国防総省の研究機関DARPAでは、あえて15年以上も前の古い設備を使って最新鋭の半導体チップを開発しているそうです。

The Foundry at the Heart of DARPA’s Plan to Let Old Fabs Beat New Ones - IEEE Spectrum

https://spectrum.ieee.org/nanoclast/semiconductors/processors/the-foundry-at-the-heart-of-darpas-plan-to-let-old-fabs-beat-new-ones

ムーアの法則の限界がささやかれる中、半導体メーカー各社はそれでもなお微細化技術の開発を押し進め、技術開発に莫大な費用が掛かるようになっています。そんな中、DARPAは微細化の流れに逆行するかのように「古臭い」製造設備にこだわって半導体開発を進めています。

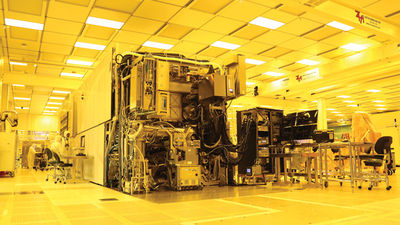

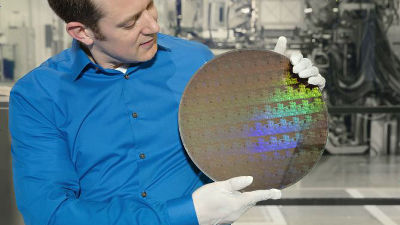

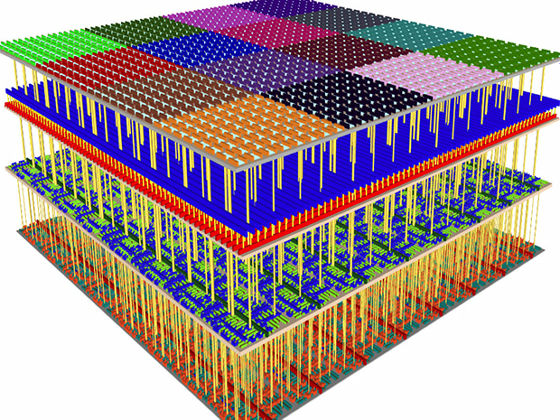

「高密度かつ高精細なモノリシックの3D統合技術を活用したコンピューティングシステム」の開発プロジェクトにおいて、DARPAは4100万ドル(約46億円)の予算を割り当てています。このプロジェクトで開発する半導体は、200mmのシリコンウエハーに90nmプロセス技術を用いて製造されているとのこと。この90nmプロセスは2004年ごろなら「最先端の製造技術」でしたが、今や「放棄された古典的な製造技術」です。

DARPAは、MITとスタンフォード大学が開発した200万個のカーボンナノチューブと100万個以上の抵抗性RAMセルを統合したCMOSチップ技術をベースにして前述のチップを開発しており、採用している技術自体は最先端のものにあたります。最先端技術をあえて15年落ちの古臭い製造設備を使って実用化しようと多額の費用を投じているというわけです。

DARPAがあえて旧来の設備を用いる理由の一つは「信頼性」にあります。DARPAに協力する半導体製造メーカーSkyWater Technology Foundryのトーマス・ソンダーマンCEOによると、従来型の技術は高い信頼性が保障されており、比較的少量のチップを製造することにも向いているとのこと。そのため、政府関係のチップの多くが90nmプロセスで製造されているそうです。

また、「安全保障上の理由」も挙げられます。最先端の技術を用いることは、特定の専門的知見に依存する可能性があり、国防技術の開発には適さないからです。また、第三者の介入を認めることは防衛技術の流出リスクにもつながるため不適当でもあります。

そして、大きな理由の一つに他に類を見ない独自技術を採用しているという「独自性」も挙げられます。前述のチップではカーボンナノチューブが半導体材料に用いられていますが、これは商業ベースの半導体材料としてはほとんど使われていない材料です。CMOSを製造するフローを一つの製造施設内で完結させることが望ましい中、一般的でない材料を用いることは、「汚染」の問題から他の半導体とのラインを共有することを困難にしており、独自の設備を用意する必要性があるというわけです。

7nm以下の超微細化技術では極紫外線リソグラフィーなどの最先端技術の開発が不可欠で、微細化技術の開発費用は年々高騰する一方だとのこと。旧来の製造プロセスを採用するDARPAの研究が成功すれば、製造法を「90nm時代に戻す」ようなものであり、半導体製造技術の底上げにもなると考えられています。

・関連記事

DARPAが考える将来のエレクトロニクス業界とは? - GIGAZINE

「ムーアの法則」の終焉は何を意味するのか? - GIGAZINE

シリコンよりも高速&省電力なカーボンナノチューブでできたトランジスタの開発に成功 - GIGAZINE

IBMが5nmプロセスのチップ製造に成功、世界初のEUVリソグラフィ実用化へ - GIGAZINE

コンピューティングの進化を支えてきた「メモリ(RAM)」は今後どのように進化していくのか? - GIGAZINE

ムーアの法則に黄色信号点滅、Intelの10nmプロセス移行の遅れが確実に - GIGAZINE

・関連コンテンツ

in ハードウェア, Posted by darkhorse_log

You can read the machine translated English article Why does the US Department of Defense DA….