半導体チップのグレードはどのように決まり、どうすれば高グレードの製品の生産量を高められるのか

「地球上で最速のAIチップ」をうたうAI向け半導体チップを開発する企業のCerebrasが、「どのようにして半導体チップの歩留まりを高めたのか」についてブログで解説しました。

100x Defect Tolerance: How Cerebras Solved the Yield Problem - Cerebras

https://cerebras.ai/blog/100x-defect-tolerance-how-cerebras-solved-the-yield-problem

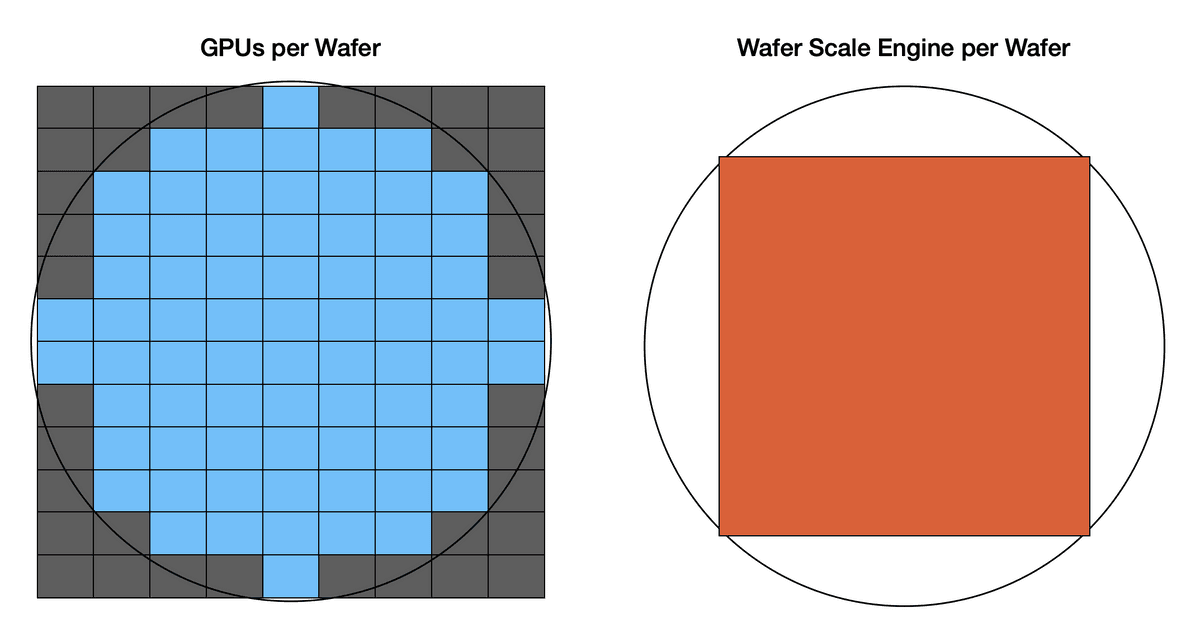

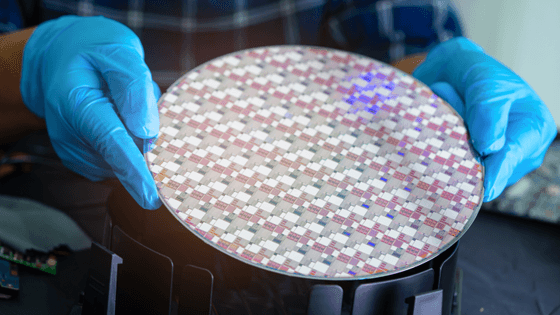

半導体チップの製造は非常に繊細で、一定確率で欠陥が発生してしまいます。半導体チップのサイズを大きくすれば性能を向上させることが可能ですが、欠陥のある領域を含んでしまう確率が高まって歩留まりが急速に低下するというトレードオフがあり、初期のマイクロプロセッサの大きさは「どの程度の歩留まりを確保したいか」によって制限されていました。

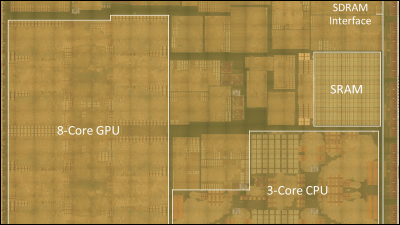

2000年代に入り、チップごとに複数のコアを持つマイクロプロセッサが登場すると、全てのコアを同一かつ独立した設計にすることで、1つのコアに欠陥が発生しても残りのコアを引き続き動作させることができるようになりました。Intel、NVIDIA、AMDなどの企業はこの「コアレベルの冗長性」戦略を採用し、例えばIntelが初めてデュアルコアとして設計したIntel Core Duoは、片方のコアに欠陥があるとシングルコア製品のIntel Core Soloとして販売されました。

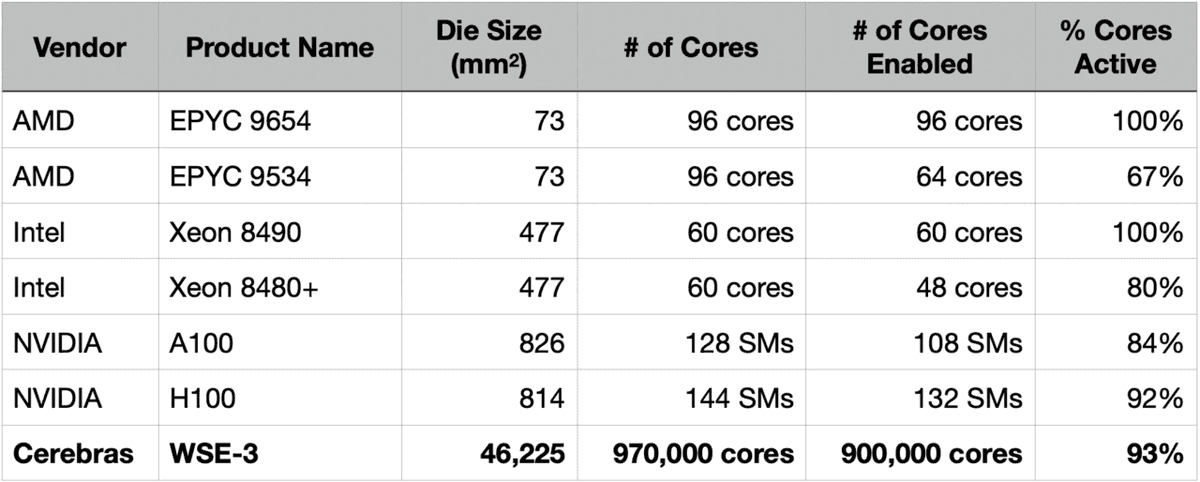

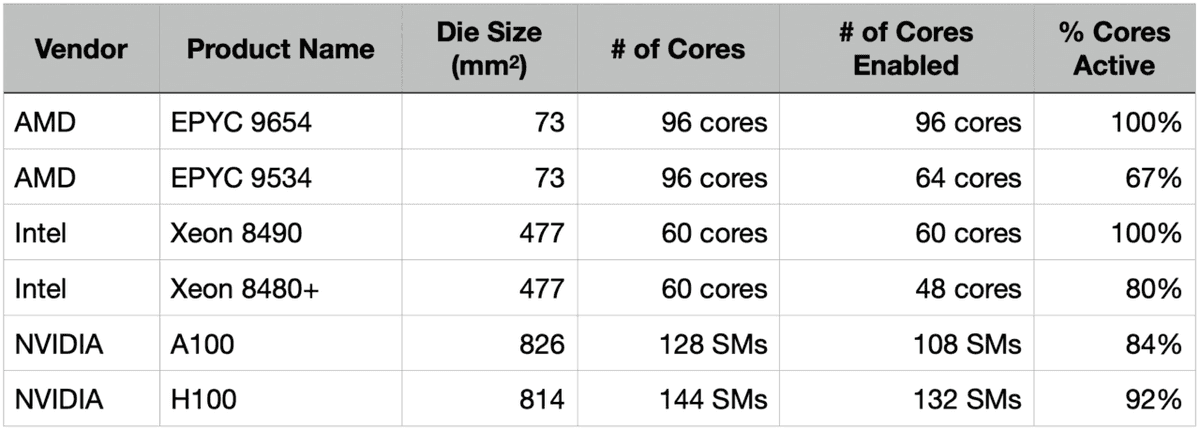

現在でも「コアレベルの冗長性」は広く使用されており、CPUでは全てのコアが有効なものをEPYC 9654やXeon 8490のような「最上位モデル」、一部のコアに欠陥が発生したものをEPYC 9534やXeon 8480+のような「廉価バージョン」として販売するのが一般的です。データセンター向けGPUは巨大すぎるため、最上位モデルでも一部のコアが無効化されています。

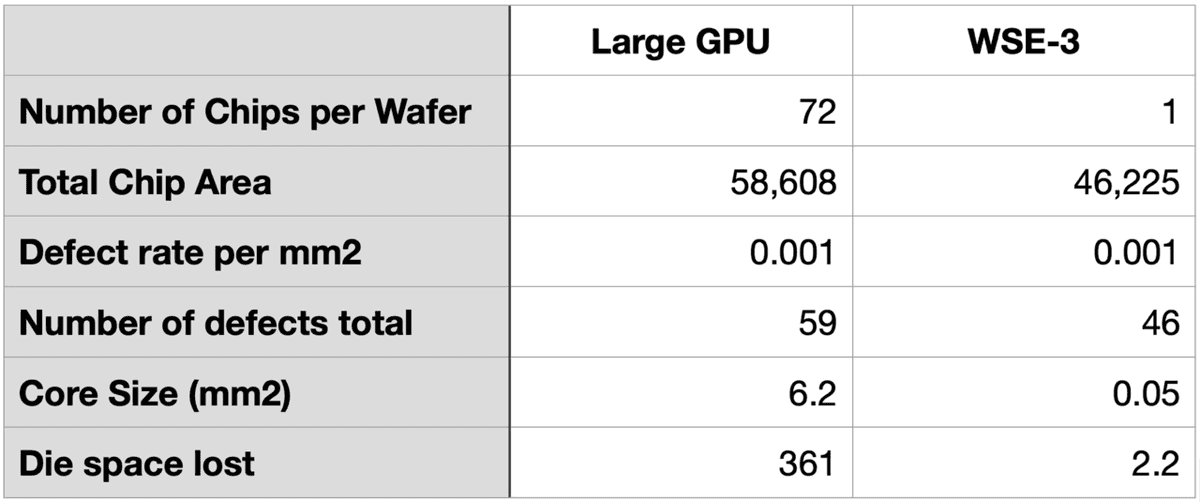

NVIDIAのH100は814平方ミリメートルという面積を持つ巨大なGPUであり、欠陥を発生させずに製造するのは至難の業です。そこで、NVIDIAはH100を設計する際、コアの管理単位であるSM(ストリーミング・マルチプロセッサ)を物理的に144個配置し、実際に有効化するSMの量を132個に抑えることで最大12個のSMに欠陥が発生しても製品として販売できるようにしました。

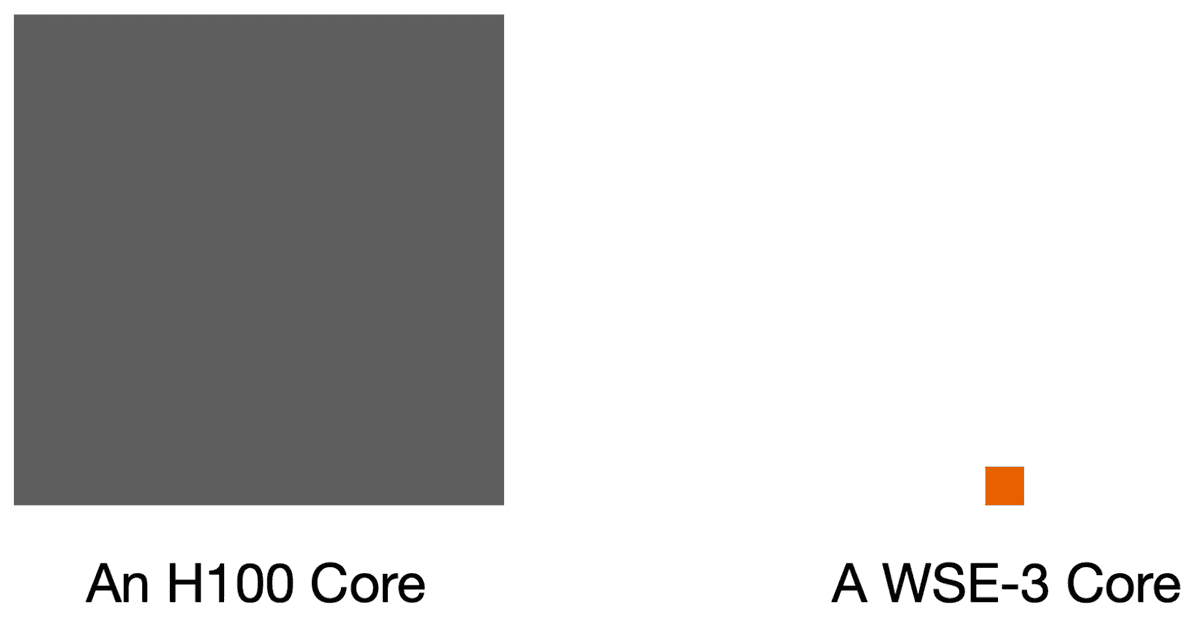

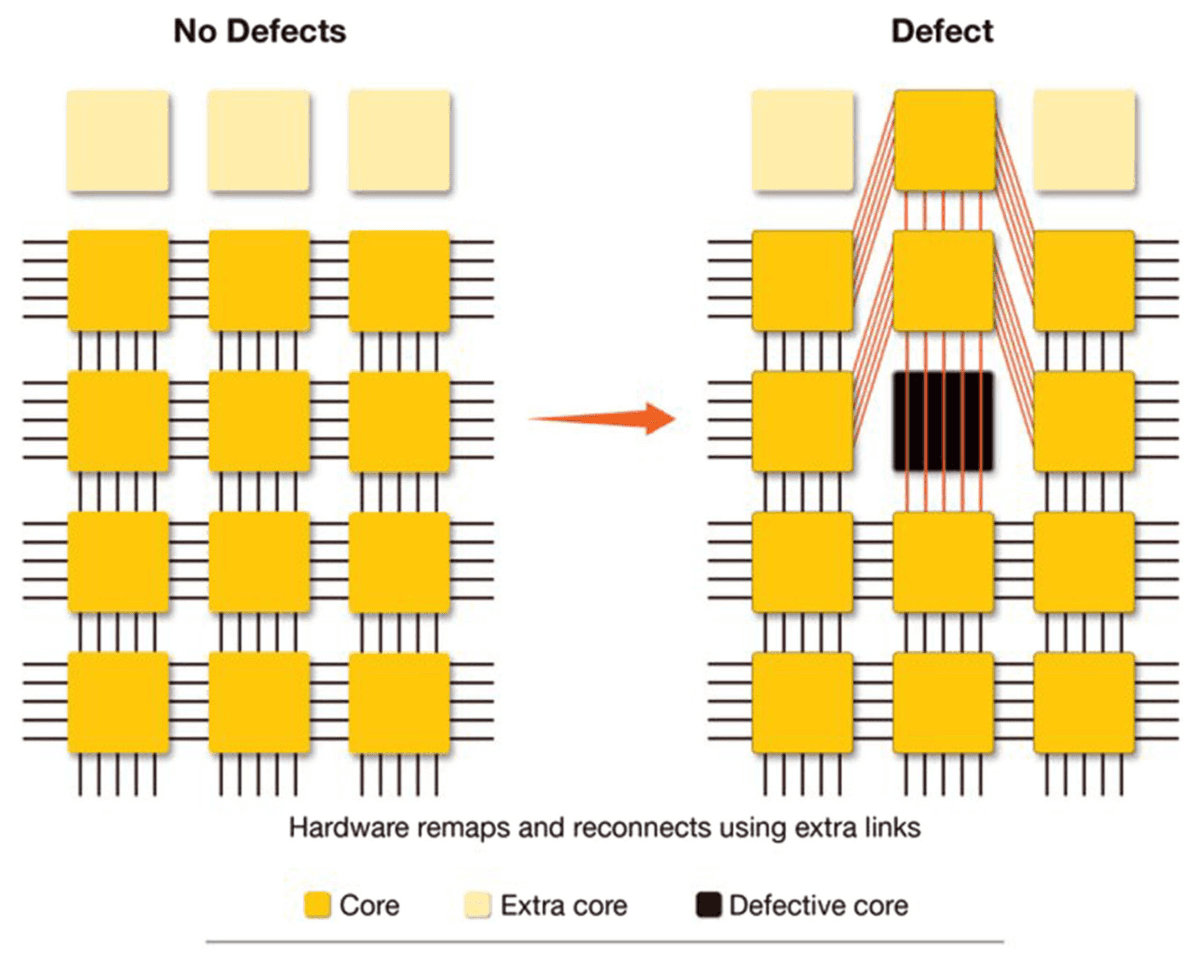

かつては814平方ミリメートルもの面積を持つ半導体チップの製造は歩留まりの問題で経済的に成立しませんでしたが、記事作成時点では欠陥を許容する設計を採用することで主流の製品となりました。欠陥が発生した際にはその欠陥を含むコア全体が使用できなくなるため、Cerebrasは「できるだけコアのサイズを小さくすることで欠陥許容度を向上させることができる」と説明しています。

・関連記事

AIのトレーニングで使用されるチップ「H100」「H200」「MI300X」の性能を比較した結果判明した事実とは? - GIGAZINE

AmazonがNVIDIAへの依存を減らすため独自AIチップを開発させている「Annapurna Labs」とは? - GIGAZINE

NVIDIAのジェンスン・フアンCEOが「AIチップ設計の欠陥は100%NVIDIAのせい」と認めTSMCには責任はないと明言、修正されたBlackwellチップは生産中 - GIGAZINE

Googleがチップ設計AI「AlphaChip」を発表、すでにスマホ向けチップやAI特化チップの設計で活躍 - GIGAZINE

TSMCがHuaweiのAIチップを製造していたことが判明、アメリカの輸出規制に抵触する可能性 - GIGAZINE

・関連コンテンツ

in 無料メンバー, ハードウェア, Posted by log1d_ts

You can read the machine translated English article How are semiconductor chip grades determ….