Micronが232層の3D NANDフラッシュメモリを発表、データ転送速度は50%高速化し2.4Gbit/sに到達

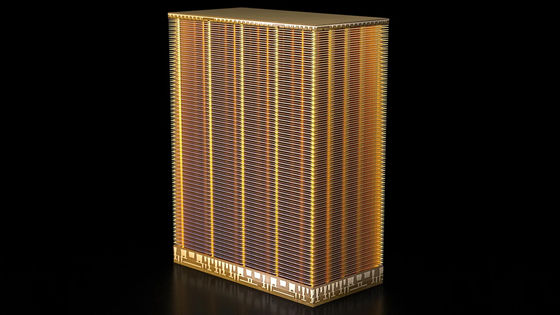

半導体製造大手のMicronが、232層の3DNANDフラッシュメモリの量産に成功したと発表しました。3D NANDフラッシュメモリが200層を超えたのは史上初で、データ転送速度は従来から50%高速化し2.4Gbit/sに到達しています。

First to Market, Second to None: the World’s First 232-Layer NAND

https://www.micron.com/about/blog/2022/july/first-to-market-second-to-none-the-worlds-first-232-layer-nand

Micron Is First to Deliver 3D Flash Chips With More Than 200 Layers - IEEE Spectrum

https://spectrum.ieee.org/micron-is-first-to-deliver-3d-flash-chips-with-more-than-200-layers

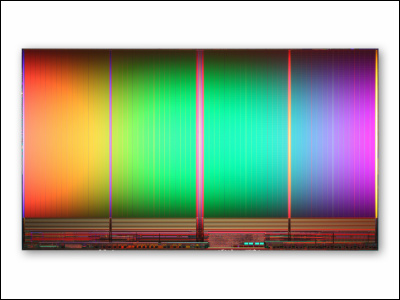

従来のNAND型フラッシュメモリを立体的に積み上げることで、メモリセルアレイを縦方向に積層化して、メモリの大容量化や書き込み速度の向上、省電力化を実現したのが、「3D NANDフラッシュメモリ」です。この3D NANDフラッシュメモリの開発では韓国のSamsung、同じく韓国のSKハイニックス、Intel&Micron、キオクシア&Western Digitalという4つの陣営がしのぎを削っているのですが、新たにMicronが232層の3D NANDフラッシュメモリを発表しました。3D NANDフラッシュメモリが200層を超えたのは今回が初で、これまでは176層の3D NANDフラッシュメモリが最大でした。

Micronによると、同社初の232層3D NANDフラッシュメモリは、競合メモリと比較して単位面積あたりに格納されるビットの密度を2倍にし、1平方ミリメートルあたりの記憶容量は14.6Gbitに到達しています。この3D NANDフラッシュメモリを構成するチップは1辺が1cmをわずかに超える程度のサイズであり、それでいて232層が集結することで大容量化に成功しています。

The next generation of #NAND technology is here — 232 layers of it. Introducing our newest and coolest storage innovation yet!

— Micron Technology (@MicronTech) July 26, 2022

More layers, maximum performance. Learn more about what the future has in store: https://t.co/TmU5l298gt #232NAND pic.twitter.com/XzVpHWc5qf

International Data Corp(IDC)の調査によると、2021年の1年間で81兆ギガバイト(81ZB:ゼタバイト)ものデータが生み出されており、2026年には1年で生み出されるデータの量が221ZBにまで増加すると推測されています。こういった状況を受け、Micronのデータセンターストレージ部門のヴァイスプレジデントを務めるアルバロ・トレード氏は、「ストレージは1年に生成される膨大なデータ量に追いつくために、革新する必要があります」と語っています。

232層の3D NANDフラッシュメモリは、Micronがこれまで展開してきたテクノロジーの組み合わせと拡張によるものです。そもそも3D NANDフラッシュメモリは、CMOSロジックとその他の回路の最下層に構築されており、読み取りと書き込みの操作を制御し、データをチップにできるだけ速く効率的に出し入れすることを目指して設計されています。バスデータの移動を最適化し、チップの入出力時の静電容量を減らすなどのレイヤー間の接続を改善することで、Micronの3D NANDフラッシュメモリのデータ転送速度は50%程向上し、2.4Gbit/sに到達したと報告されています。

3D NANDフラッシュメモリは、導体と絶縁体の層を交互に配置しエッチングすることで、深くて狭い穴を形成し、この穴部分を材料で充填します。テクノロジーの重要な制限となるのは、これらすべての層に空いた穴を確実に埋めるテクノロジーだそうです。Micronのプロセスでは、232層をまとめて一度にエッチングする代わりに、2つの部分に分け、エッチングから穴の補充までを行い、その後2つのコンポーネントを積み重ねるとのこと。トレード氏は「これは驚くべきエンジニアリングの偉業であり、我々が克服することに成功した最大の課題のひとつでもあります」と語りました。

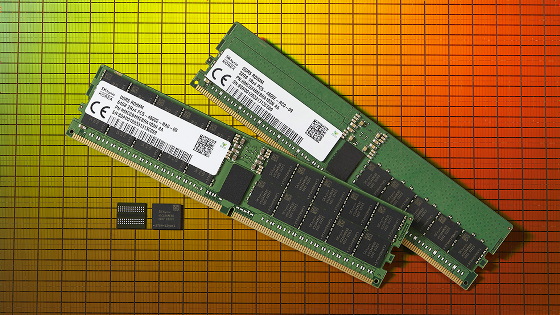

なお、各メモリメーカーはより多くの層を積載すること、あるいはひとつのメモリセルに複数のビット(bit)を格納することで、フラッシュメモリのビット密度を高めようと努力しています。Micronが発表した232層の3D NANDフラッシュメモリは、単一のメモリセルに3bitを格納できる「TLC」であり、これは既存の3D NANDフラッシュメモリの中では主流となっているものです。一方で、単一のメモリセルに4bitを格納できる「QLC」も存在しており、Western DigitalはQLC対応の162層3D NANDフラッシュメモリを発表しています。Western DigitalのQLC対応フラッシュメモリは1平方ミリメートルあたりの記憶容量が15Gbitに到達しています。また、キオクシアは2022年6月に単一のメモリセルに5bitを格納できる「PLC」技術を発表しており、より多くの層を積層する技術だけでなく、より多くのビットを格納するテクノロジーにおいても進化が続いているというのが現状です。

・関連記事

176層の3D NANDフラッシュメモリをMicronが出荷開始 - GIGAZINE

爆速メモリ技術「3D XPoint」の開発からMicronが撤退、Intelは開発継続の意向を示す - GIGAZINE

IntelのNANDメモリ事業を約9500億円で韓国半導体企業のSK hynixが買収 - GIGAZINE

毎秒9GB超と従来の3倍速度で読み書き可能な爆速SSD「Micron X100」が登場 - GIGAZINE

・関連コンテンツ

in ハードウェア, Posted by logu_ii

You can read the machine translated English article Micron announces 232-layer 3D NAND flash….