Announcing the board 'Morello' compatible with the security-enhanced architecture 'CHERI' developed by Arm over 6 years

Arm, known as the developer of the Arm architecture used for smartphone processors, has a board 'Morello' equipped with the architecture 'Capability Hardware Enhanced RISC Instructions (CHERI)' that claims to dramatically improve system security, and its own SoC. Announcing the prototype.

Morello research program hits major milestone with hardware now available for testing – Arm®

Morello Program – Arm®

Arm releases experimental CHERI-enabled Morello board as part of £ 187M UKRI Digital Security by Design programme | Light Blue Touchpaper

https://www.lightbluetouchpaper.org/2022/01/20/arm-releases-experimental-cheri-enabled-morello-board-as-part-of-187m-ukri-digital-security-by-design-programme/

Department of Computer Science and Technology: Capability Hardware Enhanced RISC Instructions (CHERI)

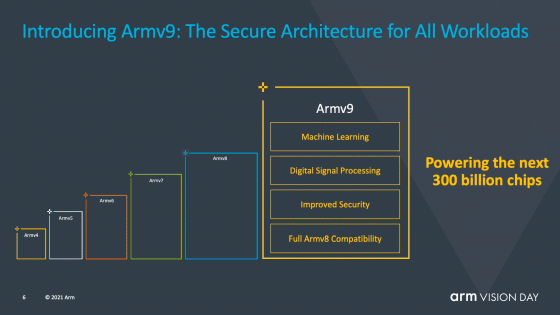

https://www.cl.cam.ac.uk/research/security/ctsrd/cheri/

Arm describes Morello as 'a focus on new design methods for CPU architectures that can better protect processors and prevent certain security breaches.' Equipped with Arm v8.2-A processor, 64-bit MIPS, 32-bit RISC-V, 64-bit RISC-V, it extends the traditional instruction set architecture (ISA) for fine-grained memory protection and scalable software partitioning. It incorporates CHERI, which makes it possible, and is useful for designing a safer computing platform.

Since 2014, Arm has been developing CHERI with the support of the Defense Advanced Research Projects Agency (DARPA), the research institute SRI International , and the University of Cambridge, and has been focusing on industrial-scale processor design. matter. Arm has positioned this announcement as a 'major milestone' and says it will ship prototype Morello boards to hundreds of companies and research institutes in the future.

A Google Research security officer who received the Morello board said, 'Computers are very useful, but their utilities are increasingly exposed to security and privacy issues. CHERI is more without performance degradation. It enables better and more cost-effective protection. ' 'For the next two years, we'll be testing the ecosystem, writing code, and co-sponsoring important feedback to determine if future versions of the Arm architecture will retain functionality,' Arm said. We have expressed our intention to develop.

Related Posts:

in Hardware, Posted by log1p_kr