PlayStation 5 built-in Zen2 & RDNA adopted SoC 'Oberon' die configuration revealed

The SoC installed in Sony's

Sony PlayStation 5 SoC die pictured up close --VideoCardz.com

https://videocardz.com/newz/sony-playstation-5-soc-die-pictured-up-close

The PS5's actual silicon processor is revealed in these first gorgeous photos --The Verge

https://www.theverge.com/circuitbreaker/2021/2/16/22285947/sony-ps5-playstation-5-die-silicon-processor-photos

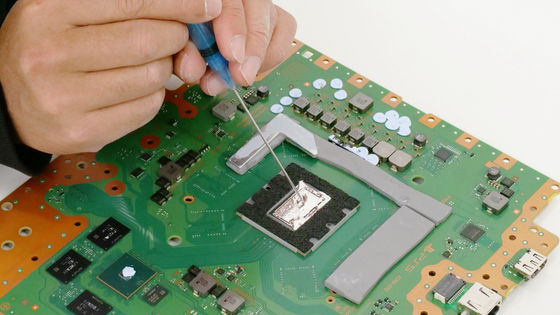

In PS5, liquid metal is used as the heat conductive material. When the PS5 was actually disassembled by the GIGAZINE editorial department, I confirmed the SoC die covered with liquid metal.

I tried disassembling the main body to find out the secret of the explosive operation of 'PlayStation 5 (PS5)' --GIGAZINE

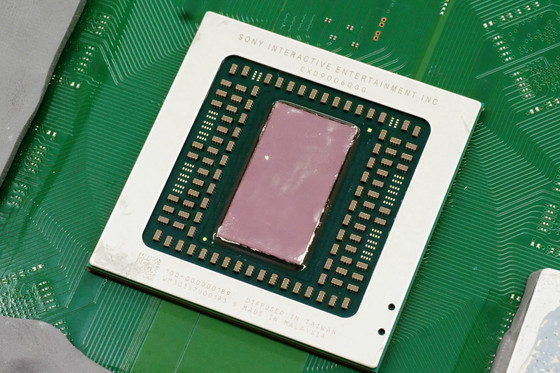

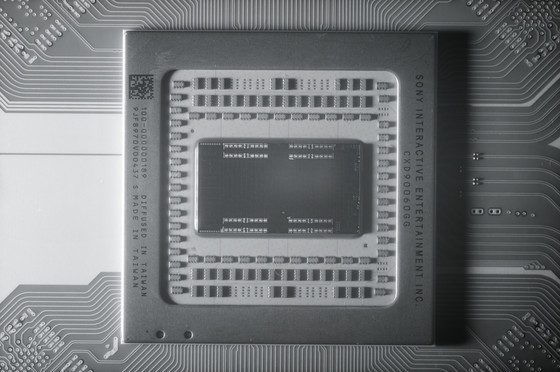

The photo below shows the PS5 custom SoC 'Oberon' that was revealed by carefully removing liquid metal and caulking.

And

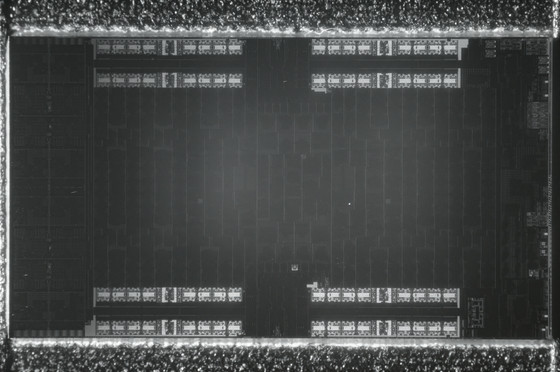

This is an enlarged photo of Oberon's die. On the left side, there are two Core Complexes (CCX), which is a core cluster that combines Zen2-based 4 cores and a 3rd-order cache. In addition, the computing unit (CU) and cache are located in the center, and GDDR6 memory and memory controllers are located above and below.

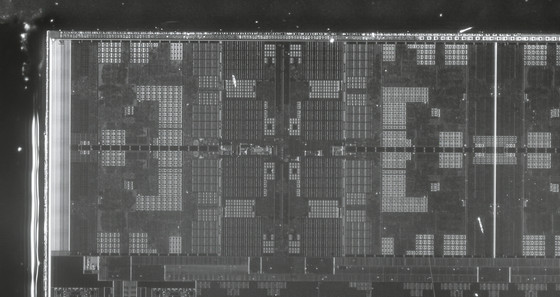

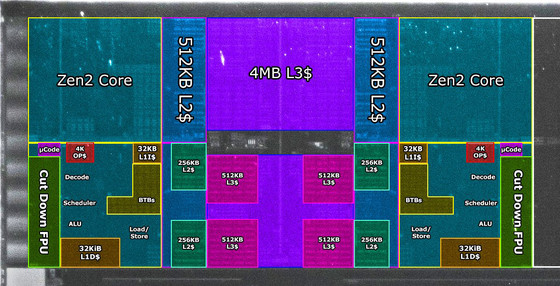

If you expand CCX further, it looks like this.

Oberon's die configuration is explained on Twitter by YouTuber's

My interpretation of the floor plan PS5 floor plan:

— Locuza (@Locuza_) February 14, 2021

1. Bomba surprise that Sony likely cut down the 256-Bit FP pipes to just 128-Bit.

2. No Infinity Cache / L3 $, also not on the Xbox Series.

3. Might have the old Render Backend design, need higher res to say for sure.

4. ... https://t.co/gwrXI903U8 pic.twitter.com/Vvmm1hGSM8

The configuration of CCX is as follows. Two Zen2-based cores are placed on the left and right, and four 512KB L2 caches and two 4MB L3 caches are placed between them.

As a result of analyzing Oberon's die composition, Locuza points out the following five points.

1: Oberon may have reduced the floating point pipeline from 256bit to 128bit.

2: The 128MB L3 cache 'AMD Infinity Cache' that was also used in the Radeon RX 6000 series is not installed.

3: The render backend, which is responsible for the final stage of the drawing process, may not be newly designed.

4: GPU consists of WGP with two CUs, similar to RDNA1 architecture. Navi 21, Navi 22, and Navi 23, which are based on the RDNA2 architecture, have only one CU for each WGP.

5: Fritz's published photos do not have enough resolution, so more detailed analysis includes details of the floating point unit (FPU), around the GPU, and the Tempest 3D Audio Engine, which is a GPU-based 3D sound processing engine. Desired.

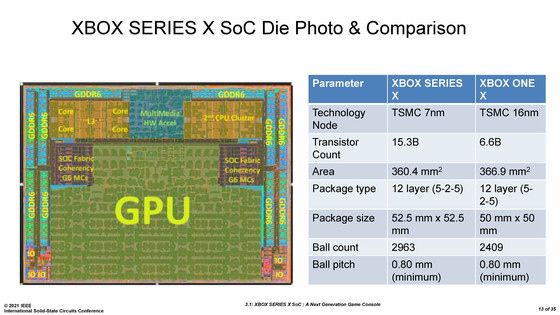

The die configuration of the SoC installed in the Xbox Series X was clarified in a lecture given by Microsoft at the

Xbox Series X SoC: Power, Thermal, and Yield Tradeoffs

https://www.anandtech.com/show/16489/xbox-series-x-soc-power-thermal-and-yield-tradeoffs

The following is the die configuration of the SoC installed in Xbox Series X.

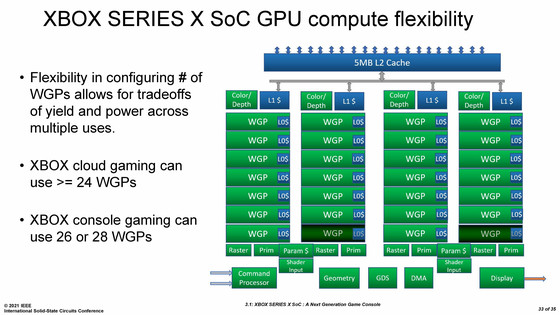

The CPU is based on AMD's Zen2 like the PS5's Oberon, and for the GPU, the Xbox Series X also has the same configuration as the RDNA1 architecture, '1WGP = 2CU', which is also the same as the PS5. The Xbox Series X has 28 WGPs, that is, 56 CUs, but the Xbox Series X sold to the general public has 1.675 WGPs in consideration of chip quality and stability. It is said that it is trying to operate 26 WGPs at 1.825 GHz instead of operating at GHz.

Related Posts: