Intel's Ice Lake generation CPU has relaxed 'maximum clock limit by instruction type'

by

Single-instruction, multiple-data (SIMD) instructions that can process multiple data with one instruction greatly contribute to the speedup of CPU operation. However, since SIMD instructions require a lot of CPU resources, Intel CPUs have specifications that limit the maximum number of clocks when executing certain SIMD instructions. This clock-down control has been a problem for some users, but research has reported that the restrictions have been relaxed in the Ice Lake generation CPU.

Ice Lake AVX-512 Downclocking | Performance Matters

https://travisdowns.github.io/blog/2020/08/19/icl-avx512-freq.html#fn:tiring

optimization-SIMD instructions lowering CPU frequency-Stack Overflow

https://stackoverflow.com/questions/56852812/simd-instructions-lowering-cpu-frequency/56861355#56861355

Skyelake generation Xeon for servers has a specification that clocks down according to the processing weight when executing AVX-2 and AVX-512 instructions, which is called 'license-based' clock down .. License-based clockdown has been seen as an issue by some users, as reported by Cloudflare in 2017, as it affects operations unrelated to AVX instructions.

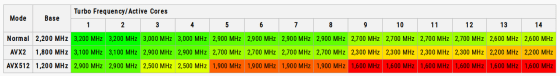

For clock down control, there are three licenses, 'L0', 'L1', and 'L2', which correspond to the 'strictness' of the maximum clock limit. L0 is the softest limit, L2 is the hardest limit, L0 license is used for normal processing, L1 is used for processing using AVX-2, and L2 license is used for processing using AVX-512. The table below summarizes the number of cores used by the program and the maximum number of clocks for each license.While the maximum number of clocks when a normal instruction is executed by one core is 3200MHz, AVX-512 instructions are When running on 14 cores, the maximum clock frequency is limited to 1600MHz.

Since the AVX-512 instruction is also installed in the Ice Lake generation CPU, engineer

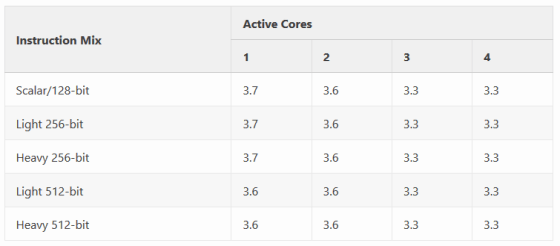

The investigation of clock down control is 'normal instruction' 'AVX-2 instruction with small CPU load' 'AVX-2 instruction with heavy load' 'AVX-512 instruction with low load' 'AVX-512 instruction with heavy load' Is executed by 1 to 4 cores and the number of clocks at each execution is measured. The results are summarized in the table below. If you execute AVX-512 instructions with 1 core, you can see a clock down of 100 MHz, but under other conditions, there is no difference in the number of clocks depending on the type of instruction.

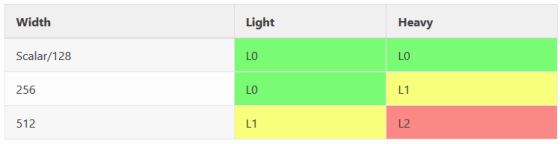

This result is due to the change of 'license allocation policy' in the Ice Lake generation CPU. In Xeon of the Skylake generation, L0, L1, and L2 licenses were assigned as shown in the table below...

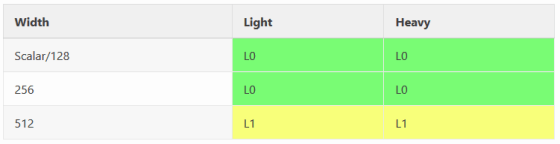

The license allocation for the Ice Lake generation CPU is as follows. The maximum clock limit is relaxed because the license for executing AVX-512 instructions with heavy processing load has changed from L2 to L1 and the license for executing AVX-2 instructions with heavy processing load has changed from L1 to L0. You can see that it is done.

From the results of this survey, 'it is necessary to change the attitude toward clock down control when using AVX-512 instructions,' Downs points out. License-based clock down control had a big impact on the entire CPU, but if you are using an Ice Lake generation CPU, 'you don't have to be afraid of down clocking,' Downs commented.

Related Posts:

in Hardware, Posted by darkhorse_log